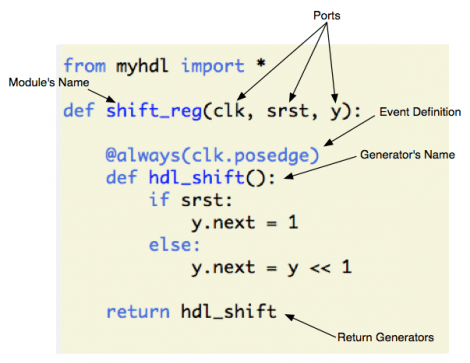

MyHDL is a Python module that brings FPGA programming into the Python environment. [Christopher Felton] tipped us off about a simple tutorial he just finished that gives an overview of how the module is used.

You may remember hearing about PyCPU a couple days ago which can run very simple Python code on a FPGA. There was a healthy discussion in the comments section comparing PyCPU and MyHDL. Although they may seem similar at first, the two are quite different. PyCPU creates a processor on the FPGA chip which can execute a small range of Python code. MyHDL actually implements Hardware Description Language in the Python environment. Once you’re used HDL to model your hardware choices in a Python script, it is converted to VHDL then fed to the toolchain and pushed to the chip like normal.

This is not an absolute beginner’s experience. But if you’re well-versed in Python it makes the jump to HDL a lot easier because you’ll be working with syntax that is already familiar to you.

I read the headline as ‘Monty Python programming option for FPGA’, was a little disappointed to discover my mistake…

This looks a lot like SystemC. I’m not sure how I feel about that. But then again, I prefer verilog, so I’m not sure my opinion can be trusted.