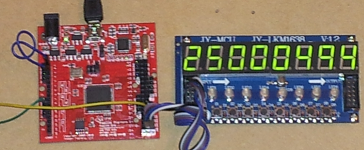

The great thing about building with gates is the crazy speeds you can achieve by using hardware directly (as opposed to working with simple microcontrollers). This 100 MHz frequency counter is a great example. [Michael] just finished building it using a Papilio board.

Of course we’re not talking about discreet chips here. The Papilio is an FPGA development board which means he is building with hardware gates, but that is still done by writing code. Above, the rig is measuring a 25 MHz being generated by a second FPGA board. Using the Papilio’s on board 32 MHz clock the device is capable of counting a frequency up to 100 MHz. You can see it measuring a 96.875 MHz signal in the video after the break. One interesting thing about that clip is that near the end he touches the crystal’s case with his finger and the Hertz really jump for a moment.

If the 8-digit display looks familiar that’s because [Michael] recently published a library to use it with an FPGA.

Cool. I like doing stuff with hardware. Always more challenging and always faster :)

Needs just an input with something like a Dual-Gate mosfet for High-Z input and sensitivity adjusting ;)

yeah baby! talk descrete components to me!

:-)

First thing that shows on google for FPGA high frequency is high frequency trading…

This is interesting.

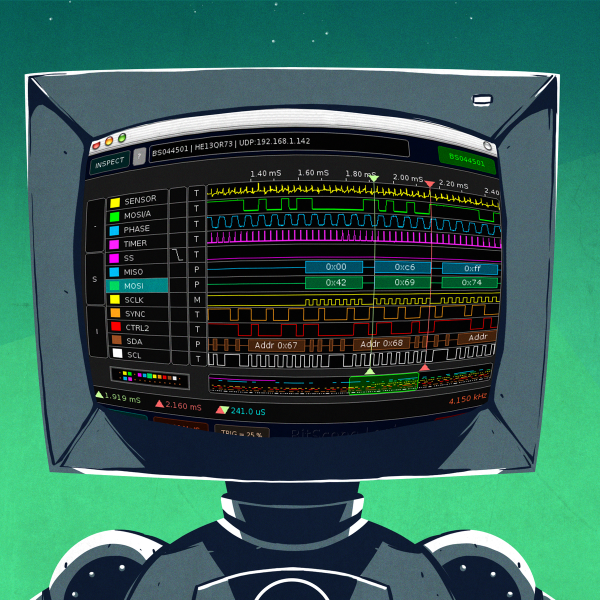

This paper ra.ziti.uni-heidelberg.de/pages/publications/papers/2011/11.pdf suggest that FPGA is sitting on top of the Ethernet and does the network stack plus the trading protocol translation.

Desition making (things that need to be more dynamic) are done on the regular computer.