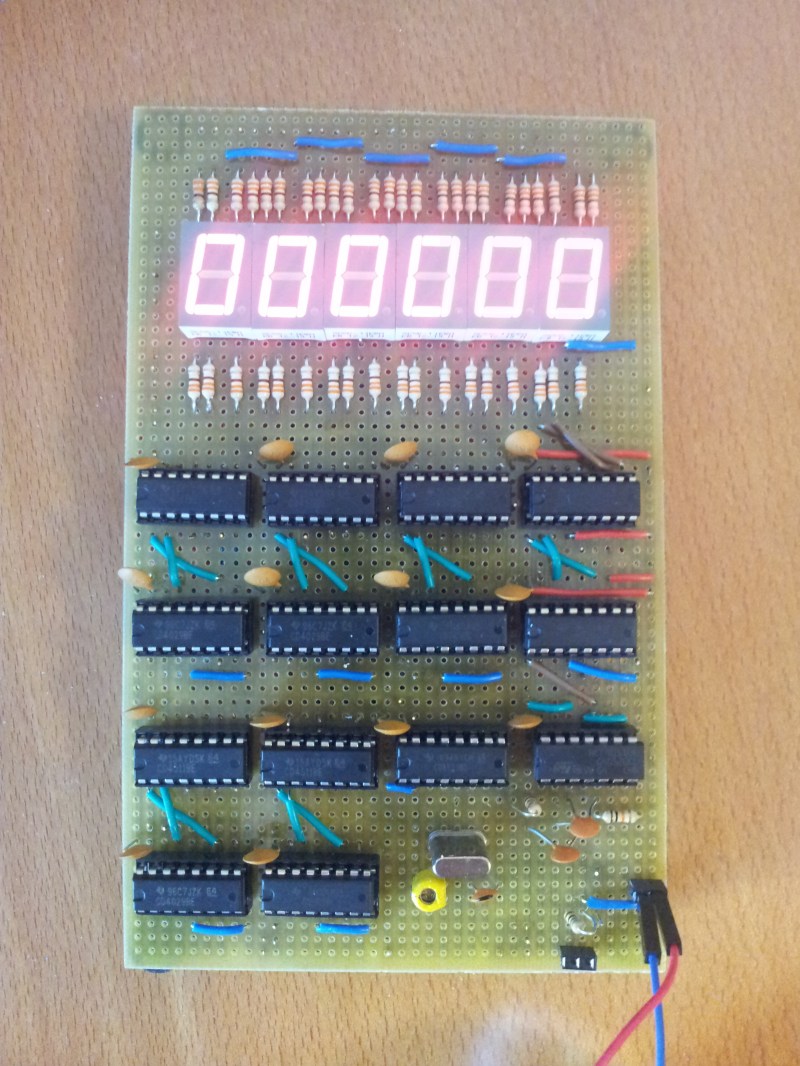

This frequency counter is [Miguel Pedroso’s] entry in the 7400 Logic contest. After looking at the design we think this is a perfect project for those who have not worked with logic ICs before. The concept is simple and [Miguel] does a great job of explaining his implementation.

At its heart the device simply counts the oscillations of an input signal for one second, then latches the total to the 7-segment displays before zeroing the counter block and starting over. Six 4029 decade counters give the device a range of 1MHz. A set of 4511 BCD to 7-segment decoders translate the count to the display. A 4521 frequency divider chip uses an on-board 4.194304 MHz crystal oscillator to time both the display latching and the counter clearing. [Miguel] mentions that tuning the load capacitors is a bit tricky. Since breadboards have their own capacitance issues it may be necessary to change the load capacitor values when moved to protoboard or the crystal won’t start oscillating. You can see those caps are not the same value, but the tests in the video after the break show that this is pretty much spot-on.

If you’d rather give this a try in HDL here’s an FPGA-based frequency counter from which you can draw some inspiration.

Looks like a fun project for me to build in a weekend :D

That’s CMOS 4000 not TTL 7400! However it looks like my old Heathkit frequency counter. That was a great project.

I noticed that myself 4000 series != 74XX

Did counter designs mid to late 70’s. Brings back memories… ^_^

Hello guys, thank you for blogging it. :)

@johnkabat

Yes the 7400 Contest is more general than only the 7400 series. You could use both 4000 CMOS or 7400 (TTL or the “newer” CMOS versions like the 74HCT series) chips.

Thank you :)

Built something similar in the Computer Lab back in 1986 (with 7400 family).

Will this work with sinewave and different analogue waveforms (at proper level) or it’s suitable just for measuring digital squarewave signal?

You could use a comparator to convert an arbitrary waveform to a square wave. Better still, use a Schmitt trigger for better noise immunity.

It’s best to put it through a Schmitt trigger first. Otherwise noise on the waveform will cause overcounting.

1 MHz? Old CMOS is wrong choice for this counter. It is too slow.

How much did this cost to build ?

Someone forgot to tell the CMOS chips that.