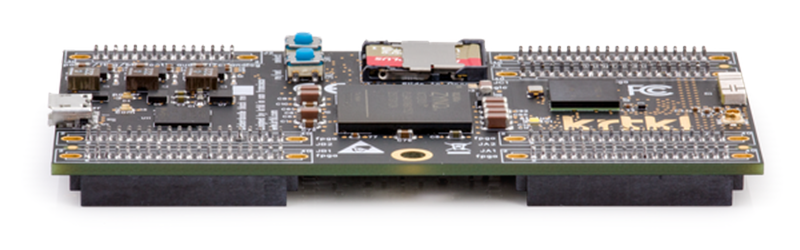

Tiny Linux computers are everywhere, and between BeagleBones, Raspberry and Banana Pis, and a hundred other boards out there, there are enough choices to go around. There is an extremely interesting ARM chip from Xilinx that hasn’t seen much uptake in the field of tiny credit-card sized computers: the Zynq. It’s an ARM Cortex-A9 coupled with an FPGA. It’s great for building peripherals that wouldn’t normally be included on a microcontroller. With Zynq, you just instantiate the custom bits in the FPGA, then interface them with a custom Linux driver. Thanks to CrowdSupply, there’s now a board out there that brings this intriguing chip to a proper development platform. It’s called the Snickerdoodle, and if you’ve ever wanted to see the capabilities of an FPGA tightly coupled to a fast processor, this is the board to watch.

The core of the Snickerdoodle is a Xilinx Zynq that features either a 667 MHz ARM Cortex A9 and a 430k gate FPGA (in the low-end configuration) or an 866 A9 and 1.3M gate FPGA. This gives the Snickerdoodle up to 179 I/O ports – far more than any other tiny Linux board out there.

Fully loaded, the Snickerdoodle comes with 2.4 and 5GHz WiFi, Bluetooth, 1GB of RAM, and an ARM Cortex A9 that should far surpass the BeagleBone and Raspberry Pi 2 in capabilities. This comes at a price, though: the top-shelf Snickerdoodle has a base price of about $150.

Still, the power of a fast ARM and a big FPGA is a big draw and we’re expecting a few more of these Zynq boards in the future. There are even a few projects using the Zynq on hackaday.io, including one that puts the Zynq in a Raspberry Pi-compatible footprint. That’s exceedingly cool, and we can’t wait to see what people will build with a small, fast ARM board coupled to an FPGA.

why oh why no onboard jtag :(

The Zybo has it: http://digilentinc.com/Products/Detail.cfm?NavPath=2,400,1198&Prod=ZYBO

I also can’t seem to find a delivery timeline of any sort.

Also: “The complete snickerdoodle schematics and BOM will be published and made publicly available before the end of the campaign.”. Sounds like an awesome product though!

Hi Mathieu – one of the creators here… The JTAG pins are indeed available on one of the headers (and on the baseboards) but we’re planning for to add a basic cable adapter (board header to JTAG) that’ll give you the standard JTAG pins. There’s also JTAG available over USB, but of course not full speed…

Hey Ryan,

Thanks for your answers!

Could you tell me more about JTAG over USB? Is it natively supported by Xilinx IDE & Vivaldo? Could you also expand on the tools required to go bare metal on the Zynq, mainly if they’re free and how complex it is to get started?

Thanks for letting me know about the shipping dates!

Depending on your answers I’d definitely be interested in being part of the alpha plan, but will only have time in a month or two (currently finishing our Mooltipass new App…)

My pleasure, Mathieu!

Re: JTAG over USB – we’re working with Xilinx for getting full support (both ARM & FPGA sides of the SoC) via Vivado. Keep in mind, this will be limited to “full speed” (not “high speed”) USB… NOTE: we also have full JTAG-over-wireless support, which is probably what a lot of people doing, say, via a wireless remote debug agent in Linux..

Re: bare metal – yes, the bare metal tools are free (Xilinx SDK + Vivado WebPACK). And we support bare metal and FreeRTOS running on Zynq out of the box. If you’re interested, you should def check out http://zynqbook.com (also free) – pretty much every example they run through uses bare metal… We’ll also be posting a number of ‘how to’ videos in the coming weeks so stay tuned!

And a couple months sounds perfect for Alpha… Just submit a “question” on the CS page and we’ll follow up.

Awesome! Do you have a typical programming speed figure when using USB full speed?

Will send you a message then… this might just be what I need for an upcoming very long project.

Oh sorry, along the sidebar under each product it gives the ship date. If you’re interested in taking part in our Alpha plan, you’ll have pre-production hardware by the end of the year – drop us a line if you’re interested…

Matthieu, no “reply” button for your last question but re: JTAG over USB…

The bottlenecks are: the USB full-speed and the SPI port. W/o stepping through states in SW, the limit is about 4.8MHz (techincally it is 6MHz with 2 bit time pauses after every 8 bits). For reference, an external high-speed professional JTAG box (that costs ~$60-250) can run to 20MHz. Figured this would be a reasonable compromise for something that adds no hardware cost…on a $55 Linux/FPGA board :)

They say March 2016, last I looked at it. It seems like a great board. It is going to be made or broken by the software/firmware support. Consider the BeagleBoard/BeagleBone: it is *ok*, but so much is left to the community. As I understand it, the whole on-die micro was just left up to the user community to reverse engineer and figure out.

The ODroid flourishes due to good mainline support from HardKernel.

Many users aren’t going to be able to go anywhere near Verilog, VHDL, or even Chisel.

So I hope they do the legwork in providing accelerator blocks for common applications, Camera framebuffer, stereovision, blob tracking, ARtag, motor control, general PID control, etc.

Otherwise, we’ll just see projects that are the usual parallel-hardware hacks: Snickerdoodle + Arduino + RasPi + Arduino + etc.

Couldn’t agree more, Andrew. We’ve architected things so people never have to even come in contact with the FPGA/Verilog side if they don’t want to. In fact, you’ll be able to load pre-build hardware configurations via your phone.

That was also part of the intention with the baseboards – to give people a number of use cases,application examples, and reference designs.

We’ll also have a bunch of IP from us/the community to help people ease into that side of things if they so choose/dare…

“This comes at a price, though: the top-shelf Snickerdoodle has a base price of about $150.”

$150 might seem expensive compared to a Raspi or a BBB but compared to other FPGA dev boards this is a REALLY good deal if you ask me.

While it might be a good deal a $150 price tag is asking a lot more than a $35 board. For a lot of people $35 is an impulse buy and $150 is not.

edit – Never mind I misunderstood the price. $55 is a great entry level price for what they are offering.

Yup, it wasn’t mentioned in the article but like Steve mentioned – it’s $55. That gets you ARM + FPGA + Wi-Fi + Bluetooth (Classic & BLE) and access to 154 I/O (230 pins by the way) – 100 of them reconfigurable…

yikes, accidentally pressed the report comment link…. sorry about that…

No problem – they haven’t booted me yet… And maybe that’ll get ’em to mention the $55 part in the article ;)

How different is this from a parallella board?

For starters, it doesn’t have a Parallela chip.

Neither does the Parallella board. (I think you are confusing Parallella and Parallax)

The Parallella board comes with a choice of zynq 7010/7020 + an Epiphany multi-core (was it 16, 32 or 64 cores?)

As I understand it the Parallella is geared towards research in many-core processors and the Zynq is mostly there to interface between the two ARM cores and the 16-64 Epiphany cores.

Hi Andre, this board is designed to be connected to the ‘real world’ – so for connecting and controlling sensors, cameras, motors, etc. Similar to the Raspberry Pi (in terms of price and size) but with 154 I/O, wireless, and an FPGA.. Hope that helps!

I sooo hope that this crowd funding campaign succeeds… I have been looking for a board like this for a year now. For a project of mine, I need 91 IOs controlled by an FPGA, Ethernet, WiFi and HDMI in in a single package. Exactly what they’re offering with the piSmasher board.

Thanks anlumo!! Sounds like the perfect for snickerdoodle. Please help us spread the word…

Their performance numbers are misleading. If you don’t use the FPGA as a processing element, say just as complex I/O, then the dual A9s will get pantsed by the RPiV2.

The parallela already has a zynq plus 16 core multicore risk cpu. They got delivered almost a year ago for 100 dollars. ok they don’t have as much oi (42) an no wifi etc but you can all add that if you need it.

https://www.kickstarter.com/projects/adapteva/parallella-a-supercomputer-for-everyone/description

Why is it $10 more to have the headers face down?

Swapping out that card is going to be a pain in the ass if you’ve got boards sitting over it.

Unfortunately, the downward-facing connectors just cost more…but we’ve decided to give everyone this option “at cost.” It was really the only way to provide reasonable access to all the I/O out of the box (without *requiring* a baseboard) but still allow for the option to plug into a baseboard for development/production.

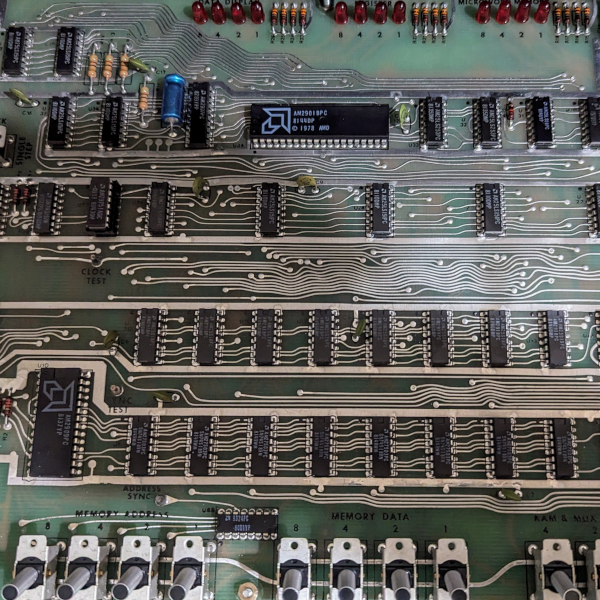

I bet “Zynq type” chips, with hardware SoC ARM cores + FPGA, will become the “standard microcontroller” of the next years. It’s so handy to have such an “universal” chip!

100% agree, RoGeorge. The nice thing is you can just treat the SoC like “another microprocessor” with tons of (custom) I/O.

I don’t think so. They’ll occupy a specific area, an important one, a powerful one, but not the “standard” one.

First of all, power consumption with FPGAs is a pretty big issue.

Second, the learning curve, both hardware and software (well, programmable logic configuration) – you can design your small ARM/AVR/PIC device with 2 months training… The proper decoupling guide for the ZYNQ is 80 pages long. Also, they come in BGAs only.

The minimal hardware around it – for a small ARM you can get away with one crappy LDO, 5 caps, one crystal and a programming header. For a ZYNQ like device you need a LOT of extra bits…

Unless these are solved, they’ll occupy a (more) powerful, but limited area of the market. It should also be noted that the combination of FPGA fabric around a standard processor is nothing new really. Although it is finally getting close to being usable by us – normal folks.

For sure, daqq. They ARM-FPGA SoCs certainly won’t fully replace all uCs/uPs any time soon (/ever?).

Of course, “depending on what you’re doing,” FPGAs can execute tasks much more efficiently than a uP/GPU. You can save a ton of clock cycles, etc. my moving stuff into hardware and of course you’re going to use fewer transistors because you only ‘turn on’ the part of the FPGA you need.

As with any new tech, the software tools are only becoming more powerful and effective at “abstracting” the developer away from the semi level. If you haven’t already, you should check out Xilinx’s SDSoC as and example. Of course it’s pretty expensive right now but give it a couple years…

As it stands right now, in my opinion there’s really no reason you should be building any kind of substantial/complex mechatronic device – namely robots, drones, etc. – using anything but an ARM-based FPGA SoC given it’s power and flexibility.

And yes, hopefully with snickerdoodle we’ve managed to take a big step forward to making FPGAs usable by us ‘normal folks’… ;)

-Ryan

Take a look at PSoC 5LP for ARM microcontroller with reconfigurable digital elelments and FPGA-like pin assignment. Easy to use too.

I really like the form factor. Unlike Pi and many other boards this board is really made to be mounted on some base boards.

Thanks, Stefan. Yes – we didn’t want to burden people with a bunch of (expensive) connectors they don’t want/need. The last thing you want in your robot/drone is a bunch of USB ports taking up space/weight…

Snickerdoodle? *giggle*

:)

yes!, they definitely wont get any entropy collisions with that search keyword.

How much are the software tools going to cost me just to get started?

$0… Xilinx SDK and Vivado WebPACK are 100% free.

Except the free Xilinx and Vivado system won’t let you get the really interesting feature of the Zynq, partial dynamic reloading.

I don’t know which Zynq is being used in this project (i haven’t looked yet) but the family supports and interesting feature that bits and pieces of the FPGA can be rewritten without turning off other parts of the FPGA. So, say you have the FPGA accelerating HDMI output, but need to use the rest for both audio and math, but not both at the same time and the space keeps you from loading both. You can, with the right tools for the Zynq family, leave the HDMI running with out stopping it’s clocks or anything, and erase the tables that contain the rest of your design and then load a different part of the design from flash. It’s a great tool, and I keep hoping Xilinx will see the light and let use makers have some access to it, but it’s probably tied up with so much NDA and other red tape that right now you need at least the educational license and a few thousand dollars to get full access.

Hey Quin (for reference it’s the 7010 and 7020) – agreed! We’re doing everything we can to twist Xilinx’s arm & get support for their *full* range of tools for snickerdoodle (SDSoC would be a killer one).

First thing we gotta do it prove to them that this is a “worthwhile” market for them to be in – as opposed to ignoring and just, you know, selling more $10,000 FPGAs to aerospace/defense contractors.

And that is ONLY going to come with volume…which is why we need support from you guys to get this thing off the ground!

too bad its only 7010/7020, no fast transceivers onboard :(

Yeah, not for this version – hard to get a part with transceivers and still sell a something with wifi/BT for $55 ;)

Hopefully we can help ‘plant the seed’ and give the maker/hobbyist world access to this stuff. That’s really what it’s all about.

Definitely something we’d like to add to the ‘family’ in the future though…

It looks like the connectors are .05″ PTH versions of Samtec TigerEye series. Couldn’t you just mount them on whichever side was most convenient while factoring in the mirroring of pin assignments on the base board? If you made the rows symmetrical with respect to power, ground edge clocks, etc, you could even make the change in solely in HDL.

It’s expensive to add, but my top additional wishlist would be a Cypress FX3 to add 350 MB/s+ data connectivity to a larger processor.

Mirroring? Pins up – sockets down is the same a sockets up – pins down.

Hi Alan/Rob – We could flip the connectors and reassign pins like you suggested, but then you’ll just be transferring the burden to the baseboard/other end? And since we have special deals worked out with the vendor (because we’re ordering *a lot* of them), it would actually end up being more expensive for the end user to do it the other way around.

As I mentioned above, we are offering this connector configuration “at cost” (the cost being the delta between male/female headers). We did grill Samtec quite a bit on these – for this exact reason – but it turns out the manufacturing on the ‘low-insertion-force’ mating connectors is much more involved, hence the premium.

Hope that helps…

TL;DR: Apparently the downwards connectors are low insertion force so you don’t have to tear the boards apart.

Exactly, a. Starts to add up when you’re talking about 270 pins! :)

For most hobbyists, one can can get quite far with a $35 dollar RPi 2 (Or even a $9 CHIP) and an Arduino. But this thing is a class all of its own. It’s for the gurus out there. I can see it being used in some fancy SDR applications, where the radio receiver can be changed on the fly on the FPGA and be backed up by the Cortex A9 cores. It can also be be used in applications requiring dedicated hardware. Couple this thing with 100MSPS ADC and you can make some mad data acquistion hardware! . Not bad for $55!

I believe similar Zynq parts can be found in the $300+ National Instruments myRIO.

Thanks, halherta! Hopefully this can help bridge the gap between hobbyists who just want a cheap Linux computer (maybe paired with a couple servos and LEDs) and the hardcore gurus… Or at least give hobbyists some upward mobility to learn/explore/build without additional cost.

NI also has the sbRIO-9651 SoM that uses a (slower speed grade) 7020 Zynq…for $800 :)

Everybody told us to just make snickerdoodle.io another RPi/Arduino/BeagleBone but we just couldn’t bring ourselves to do it. We really believe in the flexibility afforded by the FPGA and that integrated with a solid hard ARM processor this is something that the community is ready to have at their disposal.

I sincerely hope that this community finds value in what we have built and that we can go on to win together.

Good to see that you have a decent number of properly-distributed GND connections on your connectors. That’s a weak point in most FPGA boards aimed at “amateurs”. The other weak point can be power supply sequencing, but I haven’t looked at how you have addressed that issue.

Good luck with your endeavours.

Thanks, Tom! The power supply scheme is pretty clever as well. We’re actually adding a couple load switches (controlled by the MCU) to get the ‘standby’ power down to the 2 milliwatt range. Updated schematics should be available in a couple weeks…

Confirmed. I’ve added more TI load switches on the Zynq side just for this purpose — super sleep. A big shout-out/thank you to TI for supporting us on competitive power supply component pricing.

It looks like the main “out of the box” interface for this is with the (more expensive) baseboards that offload the HDMI, ethernet and USB systems. Or am I missing a way to interact with the linux SoC that doesn’t involve SSH?

Generally like the idea, just need a arduino/ATMega softcore to really push adoption; the RPi and ardunino compatible baseboards are an excellent idea (I suggest a Arduino Mega-style version too; that captures some of the 3d printer market which still often uses RAMPS).

Aussie, we would LOVE to see someone build a soft Arduino core (and would be willing to reward the first person to do so…hint hint).

You can interface with everything wirelessly or over USB. And hook stuff up using about $15 worth of connectors/jumpers. No baseboard required. Ethernet of course needs a PHY so that’s been offloaded to make sure we support all the essentials and keep the entry price (and physical size) to a minimum.

Hope that helps…

I thought The Papilio One had a SoftCore Arduino. If it did then it’s likely to be opensource.

There is, it’s called ZPUino.

You can fit hundreds of independent arduino cores in the FPGA fabric of even a modest Spartan6.

Couple of niggles. Firstly quote (1) Logic Elements (2) Block RAM and (3) DSP slices, counting gates is next to useless. Second the Zynq isn’t without competition, the Cyclone V SE has the same kind of arrangement (twin core A9s linked to an FPGA). Thirdly the Terasic DE0 nano SOC is out there already for $99 with capacity between the 7010 and 7020 models (40K LE, 2.5Mbit BRAM, 84DSP blocks)

Hi Sweeney – good points; just didn’t want to make any ‘sudden movements’ and scare people off throwing around juicy FPGA specs. The spec table in the FAQs (on the campaign page) provides data on performance metrics, LUTs, etc. And of course there is exhaustive documentation available on all this stuff.

There are a few technical reasons we ended up going with Zynq but yes, the Terasic is a solid board. Still double the cost and no wireless…or iOS/Android app. Just depends on what you’re looking for…

Ryan you have just totally killed it in so many ways on taking your time to engage as you have. And you managed to do it without even saying “super excited” and ruining it.

Thanks very much.

I appreciate that, J. Just wanted to help provide some additional info so everyone can make their own informed decisions.

All we’re trying to do is provide a product that’s usable, affordable, and that will get people building awesome stuff. Hopefully snickerdoodle is deemed worthy enough of your pledge so we can hit our goal see where this all takes us. There are probably worse ways to spend $55…

But if people think we’re full of it / would rather beat our product into the ground and talk about all the things we did wrong and all the ways it’s inferior to everything else out there, that’s fine too.

I hope you don’t mind me asking, but what “technical reasons” are you refering to?

Also, I find the Quartus software to be far superior than Vivado ISE/Xilinx SDK.

Great initiative by the way! I’m excited for this board.

“Terasic DE0 nano SOC is out there already for $99” Sounds good till you try to price just the main chip alone. http://www.findchips.com/search/5CSEMA4U23C6N

Altera is definitely good stuff, we just weren’t able to get the pricing or package size we needed to make it work on this product.

Everything about this seems absolutely fantastic, shame about the shipping for non-US people though. A $55 board to get started on with these specs is incredible, sadly that turns into $60 USD + $20 USD postage * 1.39 = $ 112 AUD for me. I know this is par for the course and definitely out of your control though, not having a whinge at the product at all – that part is totally smashing it out of the park, as well as your activity in responding to comments here, too!

I’m getting far too used to the feeling of finding some super neat crowdfunded things and then being made sad by free shipping to the US only (and usually some high percentage of the cost) and the falling Aussie dollar. Makes me wish I lived in the US sometimes.

Hi Lucas, yeah we were bummed the international shipping couldn’t be less… We’re definitely going to see what we can do to lower it once we know what our international volumes look like (potentially allowing us to work out a deal with the courier).

But thanks so much for your support! And Australia is an awesome country – I lived just outside of Melbourne for 7 years growing up. Itching to go back one of these days…

I note that products from companies like Sparkfun are sold through local companies such as Proto-Pic and others in the UK. I have no idea of the economics and practicalities, but that might offer a way forward.

Ditto the Red Pitaya Zynq scope being sold by RS.

Thanks for the tip, Tom. We’ll definitely look into this once the campaign wraps up and be sure to make some arrangements with international distributors, etc.

European companies similar to RS might include Trenz Electronic. Ditto Proto-pic and Cool Components, and HobbyTronics

Good stuff – thanks, Tom!

Thanks for the reply. I placed an order – was going to add some cables and connectors, but it added 2x $5 USD extra postage for each item! Hopefully that can be sorted out with bundled shipping and I can add some of those perks later?

Hope you’re back in Melbourne sometime!

Interesting… Yes, we’ll makes sure it gets sorted out – just be sure to add the perks, etc. before the campaign ends so we can ensure it all gets bundled together. And if you do, you can mention your previous order number or the fact that you have/are adding on to an open order in the comments. Thanks, Lucas!

Dear Ryan,

I had a somewhat related question towards pricing, not towards the thought of developing a ‘general purpose’ board as is the Snickerdoodle, but rather more application specific instances. Granted, the whole concept of the campaign is to build at a certain level of ‘scale’ or quantity– However, you’ve been able to obtain excellent pricing even with this in mind.

Thus my question: At least via all the major distributors (Digi-Key, Mouser, etc), even for the 7010, it seems they all only offer a single price point no matter the quantity– and obviously there are ways to get better price points if a certain number are ordered at once. I wondered what avenues you might suggest ? Buying from Xilinx direct or ?

Nevermnd, Avnet is (I believe) the sole Xilinx distributor in the US so we’ve been working with them. It was a bit tricky because Xilinx recently – as in right in the middle of our project – brought all their outside sales reps in house (up until recently they were partnered with guys like Norcomp for this purpose). Buying direct from Xilinx is pretty much out of the question unless you’re someone like Cisco/moving massing $$$ of FPGAs… Hope that helps!

Hi Ryan,

Your product line looks good.

I was puttin stuff in my cart (2 base boards 1 pin down and 1 pin up), the breakout and Arduino boards, + 1 set of connectors and wires. $70 USD extra to ship that made me decide not to push the button.

Hi Glenn, thanks for pointing that out – that definitely shouldn’t be the case… May I ask where you’re shipping to? I’ll ask the Crowd Supply guys to look into it.

Canada

I understand shipping can be a complicated PITA for sellers and buyers alike. Emotional responses kick in if the perception becomes that it’s not calculated fairly or when it looks like a cash grab (I am not implying that’s whats happening here).

Case in point $9 CHIP computer = $9 for product (fantastic deal) + $20 shipping (wtf) = no sale from me. I could not get past paying double for shipping then what they were charging me for the product itself. Seems like they did fix things later as they mention a %44 reduction in international shipping costs in their FAQ

Ok thanks, Glenn. And you’re right – the last thing we want to do (or, for that matter, have it appear we want to do) is have the shipping be a profit center. I can’t speak for the $9 computer guys’ business model but it’s certainly not in ours.

As you mentioned, shipping is really tricky for new products – especially when you ultimately don’t know how many you are going to be shipping and what combination of things people are going to order.

Anyway, we’ll get this figured out today. From everything we’ve seen, it’ll still probably be on the order of $20 (of course a bigger package and higher declared value than the $9 computer). But it certainly won’t be adding additional shipping for every add-on/accessory.

My Crowd Supply order confirmation mail says that I’m paying $75 for intl. shipping. That’s even more excessive.

The good ol’ US of A. The only place where online shipping costs is specified in limbs!

The only things I have bought from USA are –

1) Papilio One and LogicStart MegaWing bundled with *FREE SHIPPING** for around $100 USD because the shipping doesn’t seem so bad when it’s free.

2) 20 odd 4164 DRAMs (120ns) from Jameco because that was the only god damned place on this planet that I could find them.

3) Some tqfp chips that were sent in an envelope and actually had reasonable shipping costs.

I can buy American chips soldered to breakout boards or development boards from other countries cheaper than it costs ***JUST FOR THE SHIPPING COSTS** from the US, forget about the cost of the chip because that’s nothing compared to the shipping costs.

Like Chip $1.50, Shipping $70

I feel you.

It feels like cheaply accessible hobby electronics is really only for Americans. Is it true that you can order pretty much anything from Digikey whenever you like there for peanuts in shipping? That would be absolutely incredible.

BTW, hopefully everybody got our email earlier this week (and has had their int’l orders adjusted/confirmed) but we revamped the shipping policy to make it WAY friendlier for international orders. Check out our FAQs for details: https://www.crowdsupply.com/krtkl/snickerdoodle#faq

Hi Glenn – when you get a chance, try placing your order again. After looking closely at the order combinations, product weights, board sizes sizes, packaging, and quoted rates, we adjusted the shipping structure so only snickerdoodle has an international shipping premium ($20). If you’re ordering two snickerdoodles, shipping will be $40 but you won’t incur any shipping charges for additional items (baseboards, accessories, etc.) – in other words: everything else ships free as long as you’re buying at least one snickerdoodle.

We will be updating the FAQs to help clarify and this change will be retroactively effective for international orders (this goes for you too, anlumo!). We’ll also be sending out an email update this week letting everyone know the resolution.

Hopefully this works for you. If you have any questions or still don’t feel this is fair please let me know and I’ll be happy to discuss further.

-Ryan

Hi Ryan, earlier in the day I had placed an order for 1) snickerdoodle $55 + $5 (US) shipping x1, breakyBreaky breakout board x1, piSmasher SBC x1, shieldBuddy for Arduino x1, jumpers (50 pack) x1 and pin housings (7 pack) x1 – shipping listed at $60 – Are you suggesting i cancel my pledge and re-pledge? or can be it adjusted in the back end? Thanks for checking into this, I believe it will help with your campaign. Looking forward to getting your project funded. Glenn

Thanks for the change! However, crowdsupply does not allow canceling crowdfunding pledges (according to their FAQ), so I can’t place the order again.

Ok excellent. I’ll confirm they can adjust on the back end and let you know…

Thanks got my updated crowd supply notification.

Interesting, I wonder if it has enough power to do a QVGA versions of this, https://www.youtube.com/watch?v=zGAm8RsR1kw

In their paper it says that they are using 4 x 2 meg. Cells to do HD real-time depth maps from stereo cameras, so it could work as smoothly but at lower resolution and frame rates. http://www.bmva.org/bmvc/2014/files/paper074.pdf

Ideal for motion detection in environments where the lighting dynamics confuses standard 2D methods.

I’d have to look a bit closer at what they’re doing but you’ll be able to (relatively easily) handle a couple full-HD video streams for handling things like 3D stereo vision. Of course, you’ll need a synchronized global shutter setup – and ideally some glue logic via a PLD or something similar – but it can certainly be handled by snickerdoodle’s FPGA.

Between you and me (and everyone else who reads this…), we’re actively looking into an out-of-the-box solution for this that plugs directly into snickerdoodle that we would offer as a stretch goal. Anyway, I’ll leave it at that…I’ve said too much.

Alas, I work in a “secure” area – WiFi and Bluetooth are *Not* permitted. Guess I’ll have to stay with the Red Pitaya.

Bummer, Alan. You could always disable the radio? You’ll still be getting Zynq with 154 I/O for $55… ;)

(I’d have to do a little thinking about the possibility of removing the radio entirely…but that *could* be another option.)

If the [RF] comms were all on a separate board, AND could be physically removed, AND could not be re-installed / replaced without breaking a “tamper evident” seal…

…You’d be aiming at another target audience.

The only other security-stringent client I can think would be the Education Department, who insist that calculators are unable to communicate with each other in exam conditions.

There will be series resistors for the 3.3V VCC and 1.8V I/O supplies to the radio module which would could easily remove.

In a secure area I doubt that disabling the radio is the real problem. The problem will be the processes and procedures necessary to get *everybody* to agree that it has been disabled – and that the person introducing the equipment is not reckless and a security risk.

That’s when you gotta bust out the spectrum analyzer and too a full RF “sweep”… :)

Beyond disabling Vbat_in and Vio_in on the WiLink8 module by removing some 0ohm resistors you could remove the chip antenna if there is true concern. All of that is really fast with rework tweezers — or two irons if you don’t have those in your lab. At that point it’s equivalent to the Pitaya, since you could definitely bolt matched SMA antennas to the Pitaya RF I/O and radiate something in the FM range.

(BTW I’m one of the snickerdoodle.io designers)

You can do a one time special order the boards to have parts not populated if you have high enough volume.

Most CM have rework/modding service if you can afford to pay for it. Alternatives to removal of parts is to NC drill out the vias or tracks connecting to the radio parts.

Blue Canyon Technologies is using the Zynq as the heart of their small CubeSat. So there should be a Zynq in space sometime next year as part of the NASA CERES mission to study the radiation environment in low Earth orbit. Many more to come in the following years as more and more companies are wanting to put constellations of CubeSats in orbit.

Charles, YES! We’ll have to create our own version of the X-Prize for the “doodleSat” :)

Wow! Nice!

Xilinx please please please remove licensing from ISE.

Never going to happen thanks to US export restrictions :(

Have to get the ICEStorm guys to create free tools ASAP

What specifically about us export restrictions makes this impossible?

I’m still hoping they will remove that Piece of Sh1t DRM FlexNet and price tag considering they don’t even make series 6 chips anymore.

These parts are very complex, hope they make them easy to use.

As easy as possible, but no easier :( There is a significant learning curve both for FPGAs and for the toolset.

The toolset (Vivado) has many “magic buttons” that in effect do auto-wiring and auto-configuration, provided that they are used correctly.

Hey Ron, the nice thing about having the ARM and FPGA on the same chip is you can effectively treat it as if it were a microprocessor with a bunch of I/O. We’re going to have a bunch of pre-built bitstreams available – depending on the I/O configuration you’re looking for – that you can load over the network via your phone. You’ll (almost) be able to go the entire time using the thing without even knowing there’s an FPGA on board.

Of course, if you do want to dive into the FPGA side of things, you’ll be able to do so. Our dream would be to be able to provide everyone with free access to even Xilinx’s highest-end tools (HLS, SDSoC, etc.) so the hardware can essentially be completely abstracted, but that’s still a work in progress. In the meantime, pre-built IP & I/O configurations will let you hit the ground running without getting bogged down in Verilog/VHDL.

“We’re going to have a bunch of pre-built bitstreams available – depending on the I/O configuration you’re looking for – that you can load over the network via your phone.”

Which begs the question of the benefit of an FPGA.

Background: decades ago the team I was in was considering the benefits of programmable[*] radio parts for the generic manufacturing process. We came to the conclusion that, considering various development cycles and production costs, it was preferable to have a very flexible production line than a very flexible IC.

[*] programmable in the sense of “FPGA-like” and/or SDR

Hi Tom, the pre-built ‘blobs’ are intended to provide a basis that will cover most (at least initially) developers. Without the FPGA, you have neither the flexibility nor quantity of I/O. Both play huge roles in easing development.

At a higher level, some of the advantages of FPGAs (particularly ARM-based FPGA SoCs) in embedded mechatronic applications include:

– lower power consumption

– system (hardware) upgradability

– code portability/reusability

– system security

– greater protection against reverse engineering

– product differentiation

– hardware acceleration

– design flexibility

I am well aware of FPGA’s advantages, having first used them in 1990. But the advantages are significantly diminished by using blobs, to the extent that I question their advantage over having i/o shields attached to a processor.

It is a bit like supplying an Arduino with a number of applications; it can be done but… The real advantage of Arduinos is where you connect libraries (= FPGA IP blocks) with your C code (= your FPGA logic).

But time will tell and maybe you are onto something with the i/o blobs.

Yeah I hear ya, Tom. Nobody *has* to use the blobs. We just believe that removing as many of the hurdles to effectively using FPGAs as possible is the only way to help push their adoption into the mainstream. It’s pretty clear that just telling people to pick up a Verilog book and ‘figure it out’ isn’t the way to go…

And of course, once we get enough people building things with snickerdoodle, the numbers of ‘blobs’ will grow to eventually cover almost all combinations; and we’re moving towards people being able to “just as easily” have 100% control over each I/O pin – but one step at a time :)

The blobs will not do any harm and may well be beneficial – just like the Arduino libraries. I don’t know if it will be possible for you to have simple toolset mechanisms for combining 3 binary blobs into one “application”. If you can manage that then the blobs’ value will be significantly multiplied – I wish you well.

With the Arduino libraries, there are a limited number of books indicating how to break out of the bounds of the libraries into “pure C/C++” with RTOSs etc. Ditto FPGAs. There’s a learning curve for both bare-silicon RTOS programming and FPGA coding; IMNSHO both are worth perseverance.

ASIC economics have certainly changed in the past decade.

The FPGA wasn’t really mentioned except to say it’s there.

28k LC, 17k LUT’s, 35k FF’s (registers), 240KB BRAM and 80 DSP slices for the standard chip.

Just to clarify, those are LUT-6’s which might confuse a comparison with Lattice or older Xilinx FPGAs et. al.

IMO the approach KRTKL is taking is pretty sensible.

Consider a bare CPU chip. There are programmers at various levels of skill who can take a bare CPU in different directions: some can code up an OS and applications from scratch, some can’t. Some can code in assembly or C and some can’t. The CPU (software) ecosystem has a lot of paths one can take to make it do something interesting – code things from scratch or find built packages to help out. Some just want to install packages and start them up. The CPU doesn’t judge.

I really don’t see anything to complain about if that same sort of world evolves for FPGA. If there are those that can write every line of HDL they need to get to a goal, good for them – start up Vivado and get cracking. If there are those who just want to pick something off a menu and load a bitstream into their board so it can assume some particular hardware personality, good for them too.

Like any product, Snickerdoodle’s design made some choices in partitioning of features that make the bare module more suitable for some things than others. It’s tiny, can run off raw battery DC, has wireless, has decent CPU, has programmable logic, has a lot of IO pins. It doesn’t have a VGA or HDMI port on it, or a GPU, or MPEG encoder/decoder.

So if you have a project that already fits perfectly into a BeagleBone or RPi hardware, you might not see value in Snickerdoodle. OTOH if you started designing something on an MCU or dev board and then realized you need some hard-real-time handling on a lot of subsystems concurrently, then you might be thinking “maybe I need to bolt a dedicated MCU or FPGA on the side to really nail this problem” and then the math might change.

Thanks, Rob. Hopefully enough people like yourself “get it” and we can get the project funded. Turns out (in hindsight, unsurprisingly) when you’re doing something “new,” people just need that little extra nudge before it all clicks…

Maybe it would help if you showed more demo applications with it. My guess is that many people don’t see the potential of the Zynq.

That’s a good call, anlumo. We’re working on it!

Hi on the snickerdoodle web site they mention a router expansion board. What happened to that board?

Stay tuned, Ricardo (and good eyes)…