The semester is wrapping up at Cornell, and that means it’s time for the final projects from [Bruce Land]’s lab. Every year we see some very cool projects, and this year is no exception. For their project, [Andre] and [Scott] implemented the audio processing unit (APU) of the Nintendo Entertainment System (NES). This is the classic chiptune sound that regaled a generation with 8-bit sounds that aren’t really eight bits, with the help of a 6502 CPU that isn’t really a 6502 CPU.

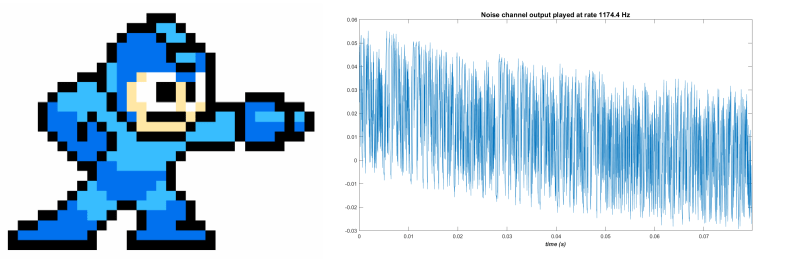

Unlike the contemporaneous MOS 6581 SID, which is basically an analog synthesizer on a chip, the APU in the NES is extraordinarily spartan. There are two pulse wave channels, a triangle wave channel, a random noise channel, and the very rarely used delta modulation channel (DMC) used to play very low quality audio samples. This is a re-implementation of the NES APU for a university lab; it is very understandable that [Andre] and [Scott] didn’t implement the rarely used DMC.

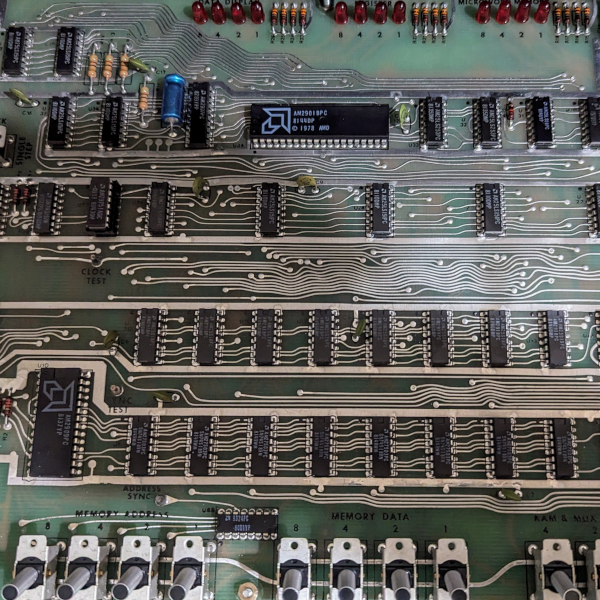

Everything about the circuitry of the NES is well documented, so [Andre] and [Scott] had a great wiki for their research. At the highest level, the APU runs on a 894kHz clock and controls three channels through dedicated registers. These outputs are fed through a mixer, which the guys scaled and combined into a 16-bit output played through a Wolfson WM8731 audio codec.

After implementing the NES APU, [Andre] and [Scott] added an SD card reader that can read the Nintendo Sound Format – the standard distribution format for NES chiptunes – and emulated a 6502 to control the registers. The result is a relatively simple device that plays NES chiptunes with amazing accuracy. The sound files on the project report sound like the real thing, but this is entirely emulated on modern hardware.

> it is very understandable that [Andre] and [Scott] didn’t implement the rarely used DMC.

If Super Mario Bros 3 (eg. drums in overworld theme) is a rare use, then I don’t know what is common…

Indeed in fact if you read the project log (which unfortunately is written at a highschool grade level) the DMC was not implemented because they ran out of time and could have a reasonable amount of music without supporting it.

Also worth mentioning is a large amount of the project is actually running in a niosii the alters softcore only the audio processing unit is HDL

Nice project. Shame about the write up but I guess luterally skills should take a backseat.

LUTerally….

I see what you did there.

Not to mention all of the Sunsoft music, with that amazing sampled bass. (Blaster Master, Journey to Silius, Batman…)

Given the number of HDL 6502 cores available why the heck did they emulate one in C?

They wanted the niosii core for SD card etc.

You can have more than one core running on an FPGA. They could have had a NIOSII and, say, a T65 on the DE2-115 they were using and still had plenty of space left for their sound chip emulation.

While the Commodore SID is a brilliant piece of engineering, it’s not an analog synth on a chip. Everything is digitally generated and fed through a single analog filter at the end of the signal path.

What did they do for the noise channel?

The original chip looks like LFSR with a selectable rate clock (input).

In the FPGA chip it looks like they have LFSR driving LUT’s that must do some sort of digital filtering??

Sorry, I can’t ready Verilog as I write VHDL.

I bought some AY-3-8912’s to play with these old sounds and then discovered that a retro computer that I have here has the same chip.