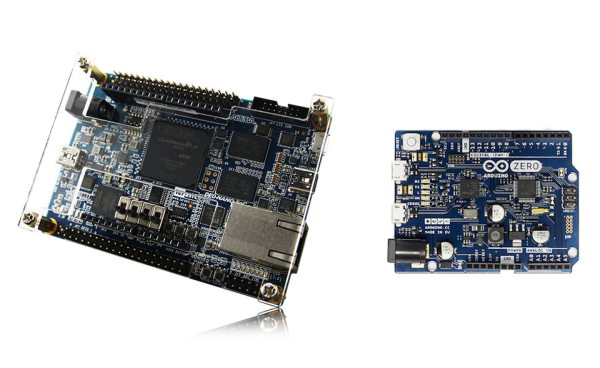

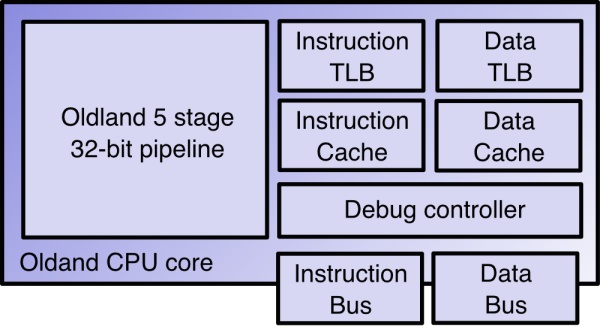

If you’ve been keeping up with the hobbyist FPGA community, you’ll recognize the DE0 Nano as “that small form-factor FPGA” with a deep history of projects from Oldland cpu cores to synthesizable Parallax Propeller processors. After more than four years in the field though, it’s about time for a reboot.

Its successor, the DE0 Nano SoC, is a complete redesign from multiples perspectives while doing it’s best to preserve the bite-size form factor and price that made the first model so appealing. First, the dev board boasts a Cyclone V with 40,000 logical elements (up from the DE0’s 22K) and an integrated dual-core Arm Cortex A9 Processor. The PCB layout also brings us 3.3V Arduino shield compatibility via female headers, 1 Gig of external DDR3 SDRAM and gigabit ethernet support via two onboard ASICs to handle the protocol. The folks at Terasic also seem to be tipping their hats towards the “Duino-Pi” hobbyist community, given that they’ve kindly provided both Linux and Arduino images to get you started a few steps above your classic finite-state machines and everyday combinational logic.

And while the new SoC model sports a slightly larger form factor at 68.59mm x 96mm (as opposed to the original’s 49mm x 75.2mm), we’d say it’s a small price to pay in footprint for a whirlwind of new possibilities on the logic level. The board hits online shelves now at a respectable $100.

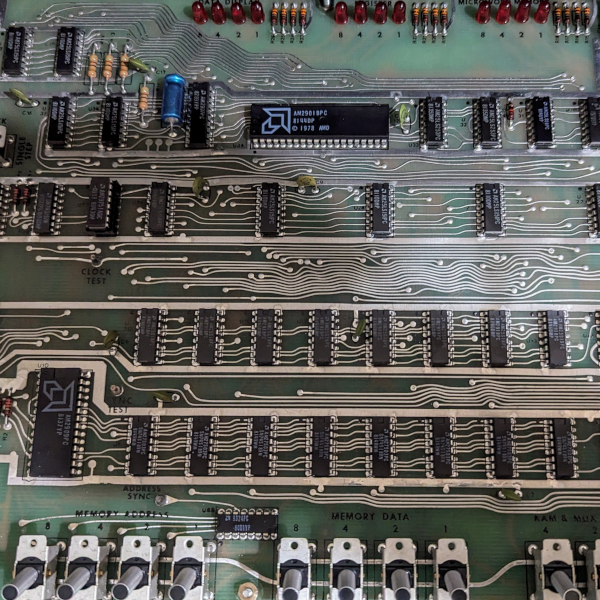

Next, as a heads-up, the aforementioned Arduino Zero finally makes it’s release on June 15. If you’ve ever considered taking the leap from an 8-bit to a 32-bit processor without having to hassle through the setup of an ARM toolchain, now might be a great time to get started.

via [the Arduino Blog]