Our friend [Hunter Scott] gave a talk at a past Supercon about phased array antennas. He mentioned he was looking for collaborators to create an antenna with the SiBeam SB9210 chip. This is a specialized chip for WirelessHD, a more or less failed video streaming protocol, and it’s essentially an entire 60 GHz phased array on a chip with both transmit and receive capabilities. For $15, it seems like quite the bargain, and [Hunter] still wants to put the device to work.

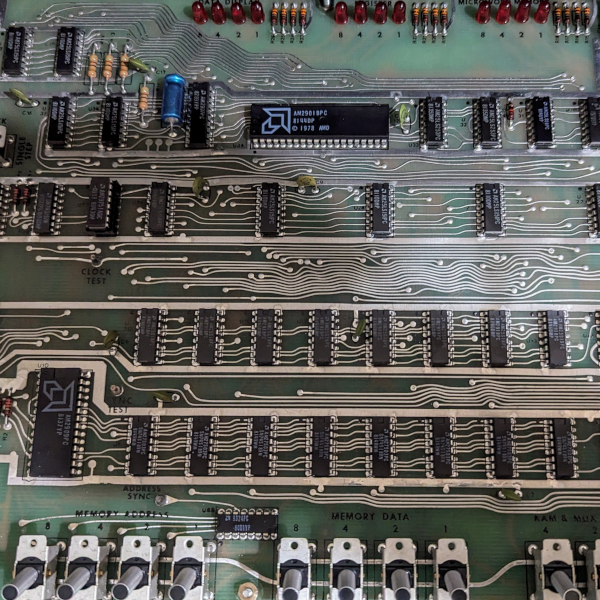

The downside is that Lattice bought SiBeam and killed this chip — not surprising considering WirelessHD never really took off. However, [Hunter] says the chip was in some old smart TVs and laptops. If you can find replacement boards for those devices on the surplus market, you can get the chip and the supporting circuitry for a song.