When we are introduced to the internals of a microprocessor, it is most likely that we will be shown something like one of the first generation of 8-bit CPUs from the 1970s. There will be the familiar group of registers and counters, an arithmetic and logic unit (ALU), and an instruction decoder with associated control logic. A complex instruction set causes the decoder to marshal registers and ALU to perform all the various functions in the right order. CPUs may have moved on in many ways since the 1970s, but the block diagram of an 8080 or similar still provides a basic grounding for the beginner.

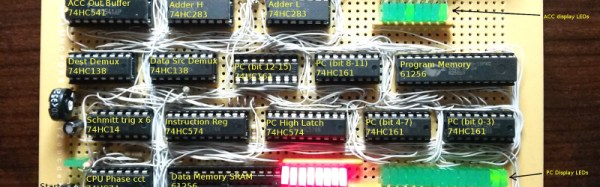

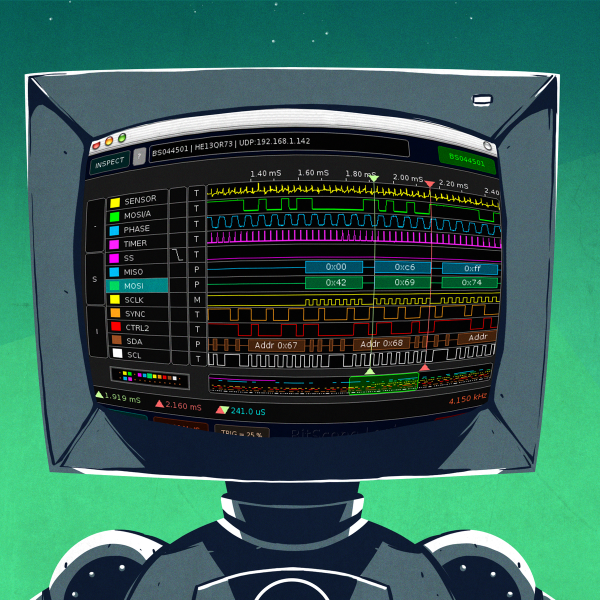

So when we tell you about another home-made CPU using TTL logic chips, you might expect it to follow this well-worn path. Fortunately though the hardware hacking community is always capable of springing surprises upon us, and [Szoftveres] has done just that with his design. It’s a one-instruction-set machine following a transport triggered architecture, and that means it deviates sharply from the conventional architecture described above. Each instruction is a move between the different physical functions of the processor, and computation is achieved by the physical functions working on the data as it is moved into them and presenting the result on their outputs ready to be moved elsewhere. The result is a computer that is in its own way beautifully simple, though at the expense of some inflexibility and lack of some hardware functions we take for granted in more conventional processors.

This machine has been built on a piece of stripboard, and has an accompanying board with display, keypad, and a modem. There is a small board based upon an ATmega8 microcontroller which performs the function of fast program loading, and can be removed once the code is loaded. Software can be written in a C-like language anc compiled using the compiler in his GitHub repository, and he has produced a YouTube video of the machine in operation. This project is well worth reading through in-depth, for its introduction to this slightly unusual architecture.

Continue reading “An 8-Bit Transport Triggered Architecture CPU In TTL”