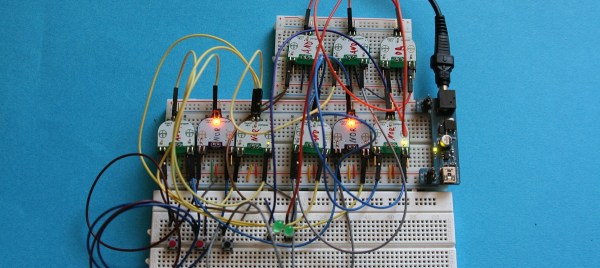

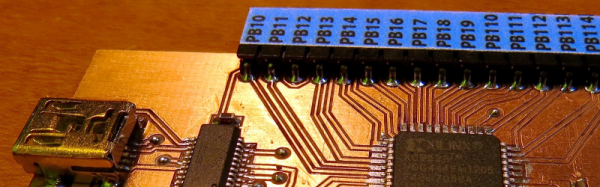

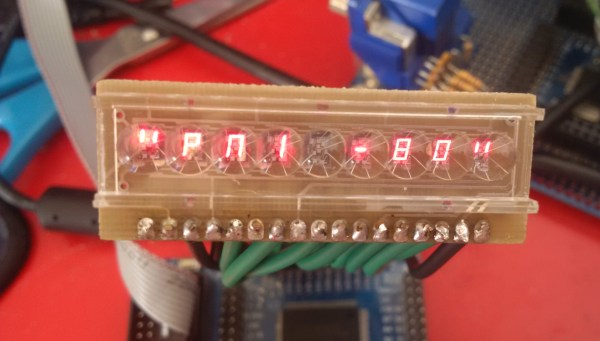

A few years ago, Philip Peter started a little pet project. He wanted to build his own processor. This really isn’t out of the ordinary – every few months you’ll find someone with a new project to build a CPU out of relays, logic chips, or bare transistors. Philip is a software developer, though, and while the techniques and theory of building hardware haven’t changed much in decades, software development has made leaps and bounds in just the past few years. He’s on a quest to build a CPU out of discrete components.

Search the Internet for some tips and tricks for schematic capture programs like KiCad and Eagle, and you’ll find some terrible design choices. If you want more than one copy of a very specific circuit on your board, you have to copy and paste. Circuit simulation is completely separate from schematic capture and PCB design, and unit testing – making sure the circuit you designed does what it’s supposed to do – is a completely foreign concept. Schematic capture and EDA suites are decades behind the curve compared to even the most minimal software IDE. That’s where Philip comes in. By his own admission, he reinvented VHDL badly, but he does have a few ideas that are worth listening to.