Since Microchip acquired Atmel, the fields of battle have fallen silent. The Crusaders have returned home, or have been driven into the sea. The great microcontroller holy war is over.

As with any acquisition, there is bound to be some crossover between two product lines. Both Atmel’s AVR platform and Microchip’s PICs have their adherents, and now we’re beginning to see some crossover in the weird and wonderful circuitry and design that goes into your favorite microcontroller, whatever that might be. The newest part from Microchip is an ATMega with a feature usually found in PICs. This is a Core Independent Peripheral. What is it? Well, it’s kinda like a CPLD stuck in a chip, and it’s going to be in the new Arduino board.

The ATMega4809 is the latest in a long line of ATMegas, and has the features you would usually expect as the latest 8-bit AVR. It runs at 20MHz, has 48 K of Flash, 6 K of SRAM, and comes in a 48-pin QFN and TQFP packages. So far, everything is what you would expect. What’s the new hotness? It’s a Core Independent Peripheral in the form of Configurable Custom Logic (CCL) that offloads simple tasks to hardware instead of mucking around in software.

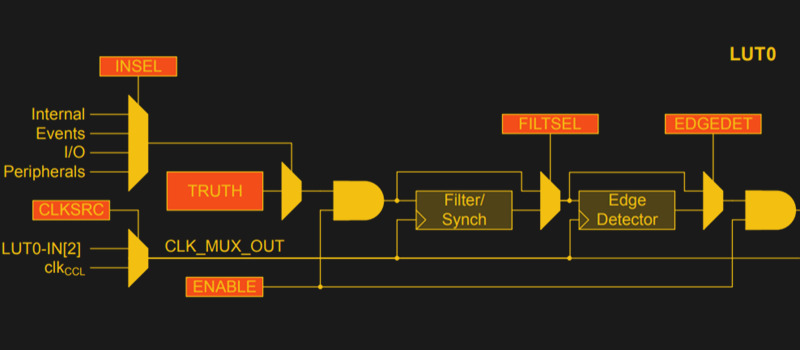

So, what can you do with Configurable Custom Logic? There’s an application note for that. The CCL is effectively a look-up table with three inputs. These inputs can be connected to I/O pins, driven from the analog comparator, timer, UART, SPI bus, or driven from internal events. The look-up table can be configured as a three-input logic gate, and the output of the gate heads out to the rest of the microcontroller die. Basically, it’s a tiny bit of programmable glue logic. In the application note, Microchip provided an example of debouncing a switch using the CCL. It’s a simple enough example, and it’ll work, but there are a whole host of opportunities and possibilities here.

Additionally, the ATMega4809, “has been selected to be the on-board microcontroller of a next-generation Arduino board” according to the press release I received. We’re looking forward to that new hardware, and of course a few libraries that make use of this tiny bit of custom programmable logic.

Yesterday at Embedded World 2018 Microchip representative also gave hints on including AVR and SAM family in the future release of the MPLAB X, but they will keep maintaining Atmel studio as well.

I use MplabX occasionally, and an import project menu entry is already there. It doesn’t work yet, tho.

Stupid question, but does this make it comprable to PLCs now like Allen Bradleys?

No

Similar stuff, but not quite. Like the gates do not work exactly like in PLC, eg. SR-latch. Also it’s pretty limited in logic size.

Just to add, yeah programming the rest of the MCU is still what it has been, ASM, C, C++ and what not.

I have some PLC experience but first I was a microcontroller guy. The PLC guys I know cower in fear when you say “structured text.” But to me you can’t count it as real programming without text files. RSLogix will let you do ladder or text or function blocks but it all just gets compiled to byte code run an extended temperature CPU. I think its a Motorola/NXP ColdFire.

So the behavior of a SR latch will be the behavior as implemented in code, not in silicon. Could you code a SR latch in ASM/C/C++, yep and the byte code might be the same as what the PLC “code” compiles to. PLCs are a joke to me except for their environmental tolerances. Where I work, all the functionality of most of our PLCs could be replaced with an Arduino Mega.

You forget the three most important things a PLC does: 1) Easy troubleshooting via visualization in ladder logic for non-programmer types 2) Ease of IO control with IO trees and smart IO cards 3) Online code changes.

I just did a project with 8K IO points with 9x AB PLCs. That would have been a nightmare to handle with an Arduino just in organization alone. Also, you can’t use an Arduino for a 24/7 process because you can’t stop the machines to do a code update. You can make that change online without stopping in a PLC

For sure PLCs are limited compared to pure C++, but that’s not the point. PLCs are really focused on massive IO coordination. Something most home users don’t need. For any serious computational crunching or data handling we use PCs with database programming and C# or Python code.

In response to the original question: A use case I would see for a PLC like scenario would be high-speed counters or safety circuits. Some things happen fast enough your code can’t keep up so you use a CCL type function to do the counting or IO response for you and then let the main program update when it loops back around. That way your response time doesn’t slow down as your program gets more complex and needs more time to loop.

As an industrial instrument tech, I program PLC’s all the time. It is definitely a form of programming, just different.

In a plant environment PLC’s are extremely versatile and built to take abuse. They provide IO protection built in and can drive a solenoid straight from the discrete output cards. They a modular in design allowing for expansion as needed.

ihayes42 makes some excellent points regarding PLC’s. Most industrial plants cannot shutdown to do modifications to the control system. PLC software such as RSLogix (Allen Bradley) allow you to make changes on the fly without interrupting the process. They make troubleshooting extremely easy as the visual ladder logic will show you exactly were your being held up in real time.

One of the huge differences I find between programming a PLC and a micro is that on a PLC you don’t have to worry about timing as much as the logic just scans over and over and you have access to a large number of timers and counters. Maybe, it could just be that an industrial process isn’t near as strict on timing as a micro might be interfacing with another IC at 20 million cycles or so.

As much i enjoy this discussion about PLCs, i kind regret my reply, since now that the limitations have been brought up, this CCL isn’t equilent to even a smart relay.

But i have to say, one of the reason ST (and SFC, CFC) is not that common is because some companies charge extra for other languages, and AB is among the worst. Ladder is good for logical stuff, but when more complex stuff, like math comes into play, it gets ugly real fast. I have done a predictive movement stuff in ST, because that was really the only way to go. There’s no way in hell i would’ve even tried doing that in LD or FBD. Same thing with communication and database stuff i’ve done.

If you want ladder programming for the MCU, there’s LDmicro.

http://cq.cx/ladder.pl (the stuff there on the download page is old stuff)

https://github.com/LDmicro/LDmicro (Here’s the current code)

Neat. Thanks for the link!

Not really! PLC are microcontroller with a huge necessity for circuit protection, adapted to be used in industrial processes. I recommend looking at OpenPLC’s project to understand how are the I/O protected and what limitation it implies (”http://www.openplcproject.com/concept-hardware”). They are commonly programmed using ladder logic, but it isn’t part of what makes them PLCs.

Nah, If you want to play with a PLC just buy a FX2N clone from Ali.

Did so myself. I don’t give a hoot about the plc software, since I’m capable of programming in a real programming language, but I found the STM32F103 and the I/O protecton very attractive for the USD 30 price point.

Ali/Ebay has a bunch of variants, with relay or transistor outputs, different connectors with or without casing etc.

They also have an onboard SMPS & common mode filter.

The only (most) crappy thing about them is the RS485. It’s an old fashioned 75176 without any external protection.

This may be premature, but will it program with usbasp?

The manual says it’s programmed using UPDI and it doesn’t mention the old SPI interface, so probably not. UPDI sounds fairly simple though, so maybe there will be a firmware update to allow the older programmers like the usbasp to use UPDI. At least, there will probably be cheap programmers available eventually once the chips using UPDI are more popular, especially if they’re gonna use it in the next Arduino.

http://www.avrfreaks.net/forum/stk500-updi-working-was-enabling-xtiny-updi

please put into 16 and 32 bit chips.

Cypres PSoC 3, PSoC 4, PSoC 5 and PSoC6 families, also with programmable analog paths and peripherials

Neat stuff, known about it for years, but never had the change (or necessity, really) to use them.

Also, this is definitely not new for Atmel; they had the FPSLIC devices like 10 years ago, which basically are a “proper” FPGA and microcontroller on the same chip.

The trouble with PSOC is the development environment. Basically nothing about it is F/OSS-friendly.

Lovely chips, but the rampant domination of the Arduino has been because of the free toolchain.

Industry doesn’t care if things are open source. Open source projects might be 0.1% of their sales.

Open source projects are 0.1% of sales for chips that only have closed-source toolchains? That’s chicken/egg.

@NateB, agreed. I actually hassled a Cypress rep a few years back about this. His reply was along the lines that nobody could possibly understand everything in the chip, etc, so you needed their tool. So dismissive…

In the next year or two, RISC-V will take ARM’s lunch, Xilinx FPGAs will be opened by the hard effort of hackers just like the Lattice parts have been, and all of this bad juju will pass.

[citation needed]

On the contrary, if you look around you, you’ll see that “industry” definitely appreciates the mindshare generated by open systems: today’s young hackers are tomorrow’s developers.

Two prominent examples are Arduino and Raspberry Pi. In the second case, I’m sure that the numbers of Raspis out there, although big for a “hobby” platform, are negligible compared to the runs Broadcom is used to. Nevertheless they seem to like the mindshare the platform gives them — after all they are slowly doling out more and more up-to-now secret specs.

I’ve messed around with the PSoC 3 a little and I think it’s a bit more in line with what you might expect when you think about a microcontroller with programmable logic, which is to say you can actually fit some useful stuff into the UDBs and the internal signal routing lets you do things like programmable logic-driven interrupts.

there is CCL in CM0 MCUs from microchip like SAML21

The ATmega4809 looks very impressive, but so does its errata… e.g.

1.2 CCL

1.2.1 D-Latch is Not Functional:

The CCL D-latch is not functional.

Work around:

None.

Of course, it’s not just a Microchip thing, and they’re not even the worst :-/

They’ve almost had me there, wondering if it was worth it to purchase their needlessly expensive, Atmel Studio supported debugger. The “CPLD in a MCU” idea sounds great, until you learn that its implementation is very limited and buggy. That makes it a no. I’ll keep fighting the Holy War alongside with my STM32 comrades.

To be fair, there are still some uses for these “logic cells” and in some other PICs and AVRs they even work as they should. I do agree that the ATMEL ICE became too expensive after Mircochip bought Atmel (I got the Basic version back then for $50, now it’s >$90).

From the Datasheet:

Configurable Custom Logic (CCL) with up to four programmable Lookup Tables (LUT). So maximally, you get 12in-4out, but you need multiple LUT’s to create Flip-flops, latches, etc. Sequential logic requires a pair of LUTs. So this might be the smallest and slowest “CPLD” there is. It’s really more like a GAL.

The smallest of CPLDs has hundreds more LUTs to play with than this device. Add to this the fact that the programmable logic is missing important features (flip-flops anyone) and I don’t think this device will worry anyone.

For not huge amounts of money these days you can buy a 32 bit ARM CPU running at hundreds of megahertz and combined with tens of thousands of LUTs on the same chip. All I can say is that this better be cheap.

It is, 1.5$ for signle ic.

First implementation that comes to mind for me is fast quad-encoder readout without needing to do the table lookups during an interrupt on the main processor. You could probably get much higher and more reliable readouts that way. I doubt whether this will compete with a 32-bit ARM CPU or a proper FPGA though.

Indeed, many 32-bit controllers (like STM32, TMS320, etc.) have either dedicated quadrature encoder peripherals, or timers with specialized modes to interface with them.

What I would like, is a microcontroller core with peripherals basically swimming in a sea of gates, which would enable you to connect anything to everything else. While I do like the STM32 series (I use the F3, F4 and F7 professionally), they do tend to be a bit limited with respect to connections between peripherals. Also, when using multiple devices via SPI, or using something that has specific requirements for the !slave select line, means you usually end up handling that in software. A bit of programmable logic would be nice for that.

Quad-Encoder was first to my mind as well. Would be nice if there were multiple on the chip to use for closed loop control of things like 3D printers.

ATMega4809, “has been selected to be the on-board microcontroller of a next-generation Arduino board”

I’m surprised as this chip doesn’t have onboard usb.

So, inferior to a PIC32MM in every way except determinism (PIC32 has a cache instead of running direct from flash).

pic32mm is an ok chip but please dont get into an 8-bit vs 32-bit pissing contest as nobody is interested.

The PIC32MM has no I2C Peripheral. Who releases a 32-bit MCU (Heck even 8-bit MCU) without at least one !2C Peripheral in this day and age?

Newer Silabs EFM8 parts have CLUs which are the same sort of thing. They also have the advantage of being ridiculously cheap.

And here i was at the start of the article, “Yay a CPLD in the same package as an ATMega! Video generation in hardware here we come!”. Now i am disappointed. :/

I wonder if those will have the same Linux non-support as Cypress ones have.

Seems pretty likely that it’ll be supported if they’re gonna put it in Arduino.

The CLC peripheral in some PIC16 (and other) series chips is a joy to use for certain tasks.

A great example is driving WS2812 RGB LEDs. If you have ever studied the working details of an Arduino library, there is some serious timing critical assembly code required to get the bit patterns right. In contrast, once the PIC hardware is set up correctly, sending data to the serial LEDs is accomplished with a simple

while(!SSP1STATbits.BF); // wait for previous serial tx to complete

SSP1BUF = databyte; // send another byte

The hardware worries about all the timing and your code is free to do other things.

I look forward to this cross pollination between PIC and AVR architecture. Each has pluses and minuses. Together, the combination could be fantastic. (Note I used the word “could”.)

+1

You can do a similar trick with the AVR using the serial port(s) but that limits which pins people can use for controlling the WS2812s so Arduino libraries do it in software for convenience.

Similarly you can control WS2812s on the Raspberry Pi while multitasking by using the audio DMA and a carefully crafted “audio” PCM stream or serial port. And you can still pump out actual audio out of the PWM or HDMI audio out.

Some Cypress PSoCs have Universal Digital Blocks that can be configured with Verilog. They are small but have enough logic to do things like quadrature decoders or other simple state machines. I don’t see how they are going to fit the programmable logic into the Arduino environment. A proper debugger would be far more useful.

I’ve had a thought of splitting an RGB LED (single NZR) signal where leg-A matches input, but leg-B is delayed by a set number of pixels. It would not take much logic to do this, but it would have to be done fast, which means not interrupt driven on an 8-bit MCU. I looked at Silego CMICs (small FPGA-style chips with 10-30 LUTs, CTRs, and others), but was only able to get it partially working. This might be just the tech I need for that. Setup the logic via the MCU, and do the timing-critical portions off-core.

Joke. You can do much more with a PsoC. Programming with a $2 cmsis-dap adapter makes it super easy and hacker-friendly.

I’d have to add the cost of a Windows license to that… I haven’t run Windows for about a decade.

I have looked at PsoC and been intrigued. It’s a shame the only dev platform is tied to Windows. I understand their focus is on professional development where an OS is a small part of the total expense, but I think overlooking the cost-sensitive hobbyist is a mistake. Passions start at home and carry into work-life.

I agree with you it’s a shame. I’m using and preferring linux too, but virtual box with a free ready-to-use virtual machine from microsoft is an option, google for microsoft vms. You can use it for 90days, free. If 90 days not enough for a hobby project I’ll be surprised. After that you can extend this period 3 times or just reinstall your VM. At least this is what I’m doing. Altough I still have my W7 licence somewhere from uni. Anyway I used FPGAs in the past and PSoC’s UDB gives me the freedom (or at least some of it) what I got with my Spartan6.

That’s an option, I suppose. Microsoft’s licensing agreement for those VMs allows such use?

“it’s kinda like a CPLD” – no, the C in CPLD stands for “Complex.” The CCL is more a SIMPLE PLD, like some fraction of a 16V8… (“perfect” for some situations. The attempts (like FPSLIC) to do larger FPGA-like combos haven’t been very successful. I bet that 4-chip Z80 system on hackaday.io could be 3 chips if it used one of these…)

“but you need multiple LUT’s to create Flip-flops, latches…” Nope; not THAT simple (which is a good thing, since there are only 4 LUTs in the CCL) Sequential logic is so common that most PLD (as well as CPLDs and FPGAs) include FFs and such as primitive blocks, so you don’t have to synthesize them from individual gates. They usually get lumped in “output macocells.” In the case of this chip, it looks like you have a couple FF-based common functions (edge detector, synchronizer) AND one configurable “Sequential Block” for each two LUTs.

(This is somewhat different than the “CLC” (“Configurable Logic Cell”) peripheral that’s in the PIC chips. (which is “interesting.”))

Nested parentheses? I’m having lisp flashbacks…

I recently acquired an Alorium Sno board. Basically an Arduino with accelerated blocks implemented in fpga fabric. Comes preconfigured with an ATmega328p soft core and Arduino Ide compatibility. There are only a few accelerator blocks available at the moment but you can write new blocks if you are so inclined.

To make a comment completely unrelated to the actual content of the article, I like that the diagram in the header has a big input box named “TRUTH”… Not sure about the philosophical implications of this :P

…going to a single input MUX. One could interpret it as “truth is the only choice”.

Or it’s just a table look up. I’m fun at parties.

Ho hum — who cares. Only the 32 bit world matters.

Just as long as I dont have to use that royal piece of crap MPLABX, they should just can that thing already. Atmel studio kicks it but all day long.

I actually prefer MPLABX over Atmel Studio. Its Microchip’s crippled free GCC compilers that keep me away from the PIC32s, DSPICs & PIC24s

Is this new? Atmel has had MCU+PL products for over 15 years, in the form of the AT94 series (AVR + FPGA on one chip). MCU functionality is probably worse (after all, they’re pretty ancient), but PL functionality is obviously far superior due to the inclusion of a proper FPGA.

Microsemi has also had MCU+PL products in their SmartFusion series for years, using a Cortex-M3 as the MCU. Microchip has announced its decision to buy Microsemi so no doubt we’ll see some Microchip SmartFusion products soon.