What would you make if you were given about ten square millimeters of space on a silicon wafer on a 130 nm process? That’s the exact question that the Open MPW program asks, and that [Matt Venn] has stepped up to answer. [Matt] came to Remoticon in 2020 to talk about his journey from nothing to his own ASIC, and he came back in 2021 to talk about what has happened in a year.

Of course, all of this hardware design isn’t possible without an open toolchain. There is an SRAM generator known as OpenRAM that can generate RAM blocks for your design. Coriolis2 is an RTL to GDS tool that can do placement and routing in VLSI. Finally, FlexCell is a cell library that tries to provide standard functions in a flexible, customizable way that cuts down on the complexity of the layout. There are GitHub actions that can run tests and simulations on PRs to keep the chip’s HDL in a good state.

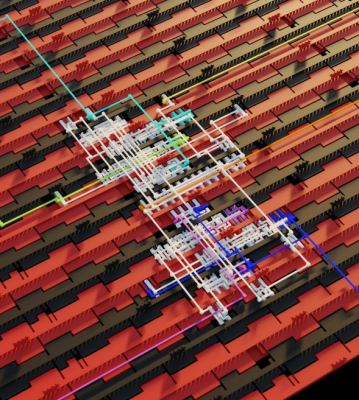

However, it’s not all roses, and there was an error on the first run (MPW1). Hold time violations were not detected, and the clock tree wasn’t correct. This means that the GPIO cannot be set up, so the designs in the middle could be working, but without the GPIO, it is tricky to determine. With a regular chip, that would be the end, but since [Matt] has access to both the layout and the design, he can identify the problem and come up with a plan. He’s planning on overriding the IO setup shift register with an auxiliary microcontroller. (Ed Note: [tnt] has been making some serious progress lately, summarized in this video.)

It is incredible to see what has come from the project so far, and we’re looking forward to future runs. If this convinces you that you need to get your own ASIC made, you should check out [Matt]’s “Zero to ASIC” course.

This isn’t the first time such a “design your own chip and get it fabbed” program is a thing, back in the late 70s and early 80s university chip design courses existed where you were able to not only design a custom VLSI chip but actually get it fabbed and turned into real silicon.

Oh that never stopped being a thing. Being democratized to being within reasonable reach of a hobbyist, though, is new.

https://en.wikipedia.org/wiki/MOSIS

Looks like there was just a single Open MPW run, in 2020?

On the front page of their website you can see that they’re on MPW-5, with wafers coming off the line this June.

At least 4 more for 2022

This is really cool, although it is important to note that unless you’re getting the $5k package, you have no guarantee of getting your chip fabbed, which is absolutely fair I have to say, the kind of information given in such a course is by all means worth that price.

So far demand has not exceeded supply, so everyone has had their designs accepted.

Since this talk, I have received my MPW1 chips which are working pretty well! See this vid: https://youtu.be/XEjc5ppRJuw

I didn’t watch that video yet but from what I can gather, MPW1 was a rough ride.

Which I think is the point ;-)

I hope to submit something, one day. I work on YGREC8 but other priorities are postponing it :-/

A FPAA that is not OTP but could be programmed by i2c, two dual op-amps, digital pots, and a 16×16 crosspoint matrix for analog interfacing

https://bit.ly/mattvenn-remoticon21 is link for presentation with a lot of links, so I’m writing it here to save somebody from retyping it from video. It would be nice if it was added to original article if possible.