Spade is an open-source hardware description language (HDL) developed at Linköping University, Sweden.

Other HDLs you might have heard of include Verilog and VHDL. Hardware engineers use HDLs to define hardware which can be rendered in silicon. Hardware defined in HDLs might look like software, but actually it’s not software, it’s hardware description. This hardware can be realized myriad ways including in an FPGA or with an ASIC.

You have probably heard that your CPU processes instructions in a pipeline. Spade has first-class support for such pipelines. This means that design activities such as re-timing and re-pipelining are much easier than in other HDLs where the designer has to implement these by hand. (Note: backward justification is NP-hard, we’re not sure how Spade supports this, if it does at all. If you know please enlighten us in the comments!)

You have probably heard that your CPU processes instructions in a pipeline. Spade has first-class support for such pipelines. This means that design activities such as re-timing and re-pipelining are much easier than in other HDLs where the designer has to implement these by hand. (Note: backward justification is NP-hard, we’re not sure how Spade supports this, if it does at all. If you know please enlighten us in the comments!)

Spade implements a type system for strong and static typing inspired by the Rust programming language and can do type inference. It supports pattern matching such as you might see in a typical functional programming language. It boasts having user-friendly and helpful error messages and tooling.

Spade is a work in progress so please expect missing features and breaking changes. The documentation is in The Spade Book. If you’re interested you can follow development on GitLab or Discord.

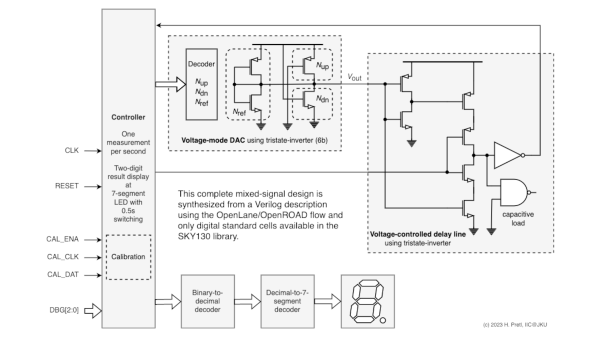

So now that you know about the Spade language, are you planning to take it for a spin? You will find plenty of Verilog/VHDL designs at Hackaday which you could re-implement using Spade, such as an easy one like Breathing LED Done With Raw Logic Synthesized From A Verilog Design (see benchmarks) or a much more challenging one like Game Boy Recreated In Verilog. If you give Spade a go we’d love to see what you come up with!