Back in the bad old days, if you needed a little bit of custom logic you would whip out a tiny chip known as a PAL. A Programmable Logic Array is just what it sounds like and is the forerunner of modern, unsolderable CPLDs and FPGAs.

PALs and GALs have died off, left to the wastes of the Jameco warehouse, and now it seems the only programmable logic you can buy are huge, 100-pin monstrosities. [Nick] at Arachnid Labs was working on his Tsunami signal generator when a user asked if they could add just one more feature: a programmable divider to count 256 iterations of a clock. This is the perfect application for dumb logic, but if you’re looking for a part that’s not recommended for new designs, you only need to look to old programmable logic.

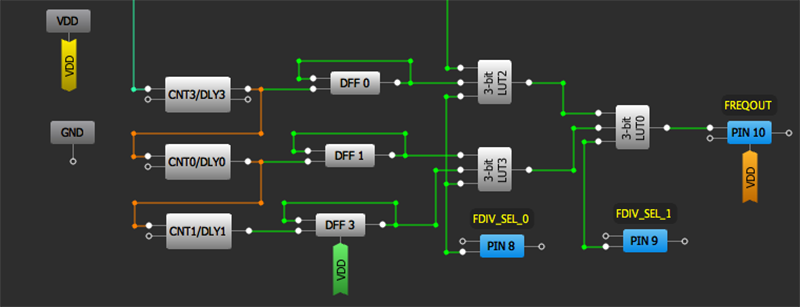

Enter the Greenpak. [Nick] had a dev kit for these ‘modern PALs’ sitting around and decided to give it a go. They’re small – they max out at 20 pins – but there are a few features that make it a little more interesting than a simple array of AND and OR gates. The Greenpak3 features analog comparators, look-up tables, RC oscillators, counters, and GPIO that will work well enough as circuit glue. They also work at 5V, something you’re just not going to find in more complex programmable logic.

These tiny chips are programmed in a graphical IDE, but the datasheet (PDF) includes full documentation for the bitstream; someone needs to write a Verilog or VHDL compiler for it soon. The one downside with these chips is that they’re tiny; 0.4mm pitch QFN packages. If you can solder that, you’re too good at soldering.

Isn’t PAL a Programmable Array Logic whereas PLA is the Programmable Logic Array, not an expert but Wikipedia makes a distinction between the two.

https://en.wikipedia.org/wiki/Programmable_logic_array

https://en.wikipedia.org/wiki/Programmable_Array_Logic

peoples front of judea vs judean people’s front.

(bloody splitters!)

Oh such a great movie!!!

Good catch.

PLA’s differ from Programmable Array Logic devices (PALs and GALs) in that both the AND and OR gate planes are programmable.

When I worked for a large manufacturer in the 70s, we had to change all of our designations of PLAs to something else due to a dispute over “PLA” and trademarks. I think the distinction between and-or arrays being PLAs and everything else being a PAL came around that time. Actually, I seem to recall we chose PAL as our alternative to PLA, and then had to change AGAIN since PAL was itself trademarked by another company. They then became Uncommitted Logic Arrays ..

22V10 GALs are still in production at Atmel and TI and in stock at Mouser and Digi-Key, in 24-pin DIP even. They are obsolete and I would only use them for a new commercial design in very special circumstances. They will be around forever from the Jamecos and surplus houses of the worlds if you want to use them in hobbyist designs or one-offs.

A part at TI doesn’t become obsolete until they say it has become not recommended for designs. And it happens they are still making as replacements the entire inventory of PAL chips that were pensioned off by AMD when they got together with MMI and eventually spun off that division and allowed it to be sold to a company who made the mistake of killing it because they thought there was no market for it. I still use PAL chips in my designs when there’s a special request for functions that are not available for regular TTL logic that I do have in my collection.

no love for cpld’s?

The XC9500XL series has decent 5V tolerant (including overshots) and much larger then a PAL. Not worth going back to PAL/GAL.

And they’re hardly “huge, 100-pin monstrosities” either. They’re available as TQFP44.

Exactly. Pin pitch is within toner transfer PCB. See myVFD driver card for old calculator display. My first AVR “Hello world” program in C was driving that. :)

http://em.motokokusanagi.com/web/Misc%20Electronics/Display/VFD/

There is a niche which is actually unfilled by anything except PALs (and actually, not even quite by them) – a dual-row programmable logic device without an exposed pad underneath it.

Why is that important? Because it provides a routing path on the board, on the same side. Modern CPLDs are *all* 4-sided parts. All of them. I was so, so hoping for the GreenPAKs, until I saw that they all have exposed pads underneath. Grrrr. PALs/GALs are handy in that sense, although still not perfect, since they’ve got one side totally dedicated to inputs, which obviously restricts what you can do. I’ve actually used a microcontroller as the world’s slowest CPLD because there isn’t any other programmable logic dual-row part with fully programmable in/outs.

I really don’t get why the GreenPak guys are all DFNs and DFN only. I mean, I get DFN as an option, sure, especially for height, but a leaded part would be so convenient, and take up less routing area.

Only the Greenpak 1 has exposed pads; the other 3 families don’t. You can definitely route them in 2 layers.

Then greenpak1 and 2 are DFN parts with exposed pads. The 3 and 4 are QFN parts. Still no way to route through (under) the chip, like a TSSOP or SOIC part.

Sorry, you’re quite right. In any case, the pin count is low enough that I don’t think breaking them out on a 2 layer board is particularly problematic.

It’s not the breakout. Breakout is easy. It’s the routing area they take up. Quad-sided parts and exposed pad parts are routing walls. SOIC/TSSOP parts have a big routing lane right through them.

One of the really useful things you can do with cheap programmable logic is fix annoying pin order mismatches (or pin level mismatches) between two chips. For instance, one chip might have a 4-bit output with its bit order “3, 2, 1, 0” on one side of the chip, and another one might have its bit order “0,1,2,3”. So now all of those stupid lines have to cross over each other, which eats up a fair amount of routing space. Obviously this is simplistic, but on a dense board with a lot of those kinds of interconnects, this can complicate the board drastically.

Dropping a 4-sided part to fix that issue helps a little, but dropping an SOIC/TSSOP part helps *even more*. It’s like putting 0-ohm resistors down as jumpers, and getting logic/pin remapping for free.

I personally have a “never route on the ground plane” policy on 2-sided boards, so tricks like this often times makes the difference between a cheap 2-layer board and a much more expensive 4-layer board.

One of the nicest thing about CPLD is that you can have the I/O pin function as you want (within routing resources and not for hardwired pins), so if you want a flow through pin out, just program it like that. You can also leave out the two side too. :P

Well, assuming that the signal you want to flow through it is unidirectional and digital.

It’s also over twice the price without factory programming, and a 44 pin package is a _lot_ larger than a 12 pin package.

I, too, love the XC9500XL series! Sadly my Xilinx disti told me that it is/was scheduled for End of Life in 2017…

I got 404 on the datasheet (PDF)

The Greenpak webpage said they are 0.4mm PITCH, I was worried that ICs are now 0.4mm in SIZE.

Haha, not yet! Ren, which datasheet on the website showed an error? I’d love to help.

The link above seems to 404’ing :(

Oh, looks like any hotlinking to our website is forbidden. But if you try copy and paste the link http://www.silego.com/uploads/Products/product_253/SLG46110r063_03272015.pdf into a new browser window – it should work.

The $20 proto PCB places in China removed the solder mask between the 0.5mm pitched TQFP pads on my last board. (I did managed to hand solder them without any solder bridges.)

Now at 0.4mm, that got to be fun.

Interesting but i cant think of many uses … i mean there are countless chips out there to do programmable dividers … hell i used a 256 4ghz divider on a single chip the other day!

The article doesn’t currently include the link to Nick’s actual post:

http://www.arachnidlabs.com/blog/2015/03/30/greenpak/

Operating Temperature Range: -40°C to 85°C

Dang. I need -40..125°C

BTW: if you need a micro and just a little bit of non-standard glue logic, then have a look at the PIC micros with Configurable Logic Cells (CLC).

Yes, if I were using a more modern processor in the Tsunami, I probably wouldn’t have needed this. My personal favourite is the Cypress PSoC range, which could also manage this in internal logic.

Bad old days? PALs/GALs were fantastic! You ould replace so many 74HC (or whatever family) pats with them and save so much space, not to mention fix for logic and wiring errors by programming. One the GALS came out and I wasn’t thoowing away a chip with every mistake, it was heaven. How about a PALASM assembler for the new devices?

I have a full tray of XCsomthing I got for free. TQFP44 I think. I assumed I needed a special programmer and they have just sat in their fancy frame.

I once used some 22V10 and 16R8 parts to turn a 68000 bus interface into a VME bus interface, saving quite a bit of money for my employer at the time.

Alas, a trick that’s not very useful today…

XC9500 series? Those program (and reprogram!) over JTAG. Pretty straightforward.

I use Verilog and ispLEVER Classic from Lattice to generate .jed files for GALs, that I still use in new designs. OK, they aren’t modern designs, since I am stuck in a world of pin-in-hole and sockets, but I find GAL22V10 and smaller devices really useful. My last design was for an Atmel 328 powered MIDI interface, which drives a flourescent display, has switches, pots and LEDs on it. To save pins on the processor, I developed a small I/O bus and assigned a few pins to address the various devices. A GAL is perfect for decoding, and a bit of latching as well for displaying status on LEDs without dedicating pins. I bought up stocks of GALs from a certain auction site when they were being dumped by someone. I have an ancient ALL-11P programmer which only claims to work with Windows, but like ispLEVER Classic, runs in WINE on Linux very well. I’ve also used GALs to program up a replacement for certain older devices where I can’t find a replacement part – like for the equally ancient HP frequency counter with Nixies I use. I’ve also repaired some classic early digital synths that way too.

Sheesh, I must be getting old.

Sigh. I bought some of the 8-pin initial greenpak chips, and their development board, and made some breakouts, and I guess they went “not recommended for new designs” before I finished figuring them out.

Using one of the CLC-equiped PICs solely as a low-pin-count programmable logic chips is also an interesting idea. Cheap and low-power by CPLD-standards, too. Not quite as much IO as I’d like.

To all you who can’t think of any reasons to use PALs–

That’s because you can’t do–read “don’t know how to do”–true logic design.

When was the last time you designed a small, custom parallel logic system from a few gates; or a complex state machine from a small number of chips.

The Electrical Engineering world does NOT revolve around hacking some (usually-not-the-best-choice-anyway) microcontroller with pooly-designed code until it ‘kinda’ works.

“The most elegant and best design occurs not when there’s nothing left to add, but only when there’s nothing left to remove.” –anon

That’s because we aren’t all EEs. CEs and CS and artists might decide to follow the same mantra in the design, and code, but use a slightly more powerful part just in case something gets added to the design spec at the last minute.

In the CompSsci world, “Make your code O(n log(n)) or better where possible, but over spec the CPU at least double because what ever data set you designed for is the smallest set that will end up being used.”

“Make your code O(n log(n)) or better where possible”

I’ve never seen any consideration of algorithmic complexity in my commercial experience. Instead, commercial development time constraints usually lead to people implementing the quickest, dirtiest solutions, employing as much off the shelf (assumed to be best) code. Consider the proliferation of table-driven CRC-16 implementations or CRC-16 single-bit implementations, when the byte-parallel versions are almost as short as the single-bit versions and almost as fast as the table-driven versions (byte parallel CRC for AVR follows):

ushort CrcCCIT16(ushort crc, byte data)

{

ushort tmp0=crc;

asm volatile(“mov %A3,%B4\n”

“mov %B3, %A4\n” // crc = (unsigned char)(crc >> 8) | (crc <> 4;

“mul %B4,%A3\n” // (crc&0xff)<<4.

"eor %B3,r0\n" // crc ^= (crc << 8) << 4; (r0 wonderfully contains the other 4 bits)

"ldi %A4,32\n"

"mul %A4,%A3\n" // (crc&0xff)<<5

"eor %A3,r0\n"

"eor %B3,r1\n"

"clr r1\n" // crc ^= ((crc & 0xff) << 4) << 1;

: "=r" (crc), "=r" (tmp0) : "r" (data), "0" (crc), "1" (tmp0));

return crc;

}

The main code takes 16c and 26bytes to implement [it's part of FIGnition's audio loader]. Although it uses mul three times, it multiplies by 16 or 32 and that's easily converted to nybble swapping instructions or relatively efficient bit-shifts on other processors.

So, why does table-driven CRC code dominate? Because when people want to do CRCs, they just pick the first solution they find on the net: they figure O(1) thinking is more important than O(anything) in the CPU; because Moore's law will solve the rest. That's the real reason they use more powerful parts – today we just chuck as much computational power as possible at a solution to avoid having to think.

O(n.log(n)) is a good principle, but it needs to be applied all the way through the system. Consider an O(n.log(n)) method that uses an O(n^2) sub-procedure. The result will be: O((n^2).log(n^2)) = O(n^2.2log(n)). The n^2 has propagated to the top level. I shouldn't really include the 2log(n), it should be just log(n), but it's worth thinking about. That 2 is a whole iteration of Moore's law, two whole years of technological potential wiped out in a single method.

For these kinds of reasons it would be much wiser for people in the industry to follow RService's advice, the best design decisions are the ones where you find you can remove something.

Why does Hackaday keep spreading this attitude that SMD parts are somehow off-limits to hobbyists? True, 0.4 mm does pose some challenges to the typical hobbyist PCB process, but with a factory-made PCB it is pretty simple to solder after a bit of practice.

Nothing “too good” in it, just a few hours of practice like any other part of the hobby. Good tweezers, suitable tip and some flux help – shouldn’t cost more than $20 on eBay.

It’s 0.4mm pitch *and* a QFN package. That’s a lot different than soldering some 0604 resistors.

Yeah, in some ways, it’s easier. Definitely easier than QFPs.

If you work with SMD parts, especially QFN parts, you need a hot-air rework station with a preheater and a supply of solder paste. Preferably a paste dispenser as well. This isn’t really high-cost equipment anymore, although as always, the more you spend the nicer it gets. But you can do perfectly good soldering with a $100 rework station off eBay once you get used to it.

If you’re trying to solder with an iron, yeah, it sucks, I agree. So don’t do that.

Then putting on QFNs is just as simple as laying down a line of paste around the edges, placing the part, heating until the solder is liquid, tap the part to make sure it’s aligned and in tension, and tap the top to push any excess solder to the outside. Then a fine-tip iron can clean the thing up easy.

How is it easier? Because the parts aren’t as small, and have a ton of terminals so surface tension is much stronger (Takes longer, of course, but I said ‘in some ways’).

>PALs and GALs have died off

>100-pin monstrosities

Hello ?

TI PAL are still tagged as “active” in their website (as of april 3rd 2015).

http://www.ti.com/sitesearch/docs/universalsearch.tsp?searchTerm=TIBPAL16L8#linkId=1&src=top

Did you by chance see my comments from earlier? I stated much the same thing.

Does anyone know of a graphical programming environment for CPLD or FPGAs for beginners? Something similar to Labview where ready made blocks of various complexity can be wired together and attached to the pins on the device would be great.

What you’re describing is pretty much the Greenpak Designer software. For more sophisticated devices, all the major manufacturers offer something like this, of varying quality and usability; I haven’t tried it myself.

I’ll take a look at the Greenpak software. Thanks for the tip. I noticed Labview has an FPGA programming software module, but it only works with National Instruments FPGA boards, and they are pretty expensive.