Munged Ferris Bueller quotes aside, Conway’s Game of Life is the classic cellular automata that we all reach for. The usual approach is to just iterate over every cell in the grid, computing the next state into a new grid buffer. [K155LA3] set out to turn that on its head by implementing Game Of Life in the hardware of an FPGA.

[K155LA3]’s version uses Chisel, a new HDL from the Berkley and RISCV communities. Under the hood, Chisel is Scala with some custom libraries that know how to map Scala concepts onto hardware. In broad strokes, Verilog and VHDL are focused on expressing hardware and then added abstraction on top of that over the year. Chisel and other newer HDL languages focus on expressing high-level general-purpose elements that get mapped onto hardware. FPGAs already map complex circuits and hardware onto LUTs and other slices, so what’s another layer of abstraction?

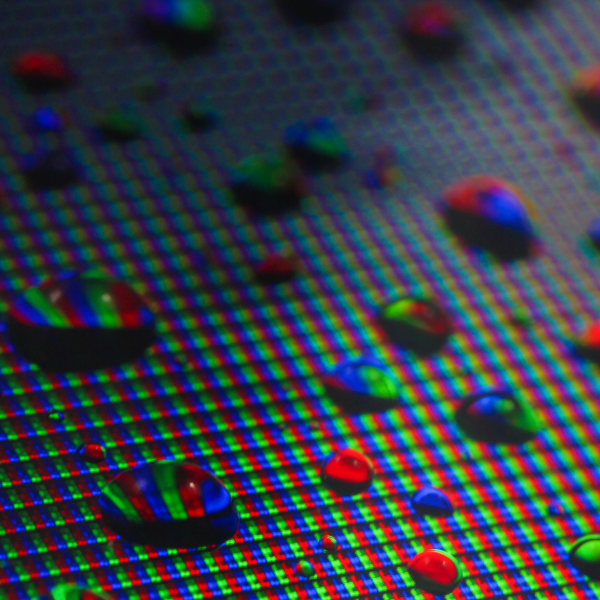

The FPGA chosen for this project is a Digilent Arty A7 with a VGA Pmod to turn the RGB444 into analog signals to actually display. What’s impressive about [K155LA3]’s implementation is just how fast it is. Even running at 60 frames per second it’s almost as fast as the monitor can handle. Of course, most computers lying around you could simulate a 60 x4 8 grid at 60 fps. Next, instead of connecting the grid logic to the 60 Hz VGA clock, he connects it to the 100 MHz board external oscillator. Now each pixel in each frame displayed contains over a million generations.

Unfortunately, even this small grid of 60×48 takes up 90% of the LUTs on the Artix-7. In the future, we’d love to see an even larger FPGA hardware implementation capable of handling grids that could hold whole computers in them. And naturally, this isn’t the first FPGA version of the Game Of Life here at Hackaday.

LOL it’s all LUTs. 90% on an Artix 7.

Dare I say – too much parallelization.

If the VGA has to go out sequentially at a fixed rate then it makes sense to use address multiplexed serial processing and a much much smaller FPGA.

It’s only too much parallelization if it becomes a limiting factor. For the selected platform it seems quite limiting but for a MUCH bigger FPGA it would be a sane choice. Now just to buy a couple $25K FPGAs. :P

SQRL Acorn could be a cheap option to expand that experiment. Artix 7 200T for $70 or so, one of the biggest FPGAs supported by the free license.

An exercise for the student: assume a 17″ VGA display, with a glider gun in one corner of the grid. How fast are the gliders travelling as they zoom across the display? (at least until they destroy the gun as they wrap around the torus)

“What’s another layer of abstraction?”

A waste of LUTs. The Game of Life is not hard to implement in VHDL or Verilog. The logic of Life-like games is already pretty simple (count live 8-neighbors, change state based on the count).

In terms of implementation… If you brute force it in a single clock cycle, it will eat LUTs, even without unneeded layers of abstraction. You could also slow things down, imply a MUX and a counter to handle the neighbor counting across 8 clock cycles, then perform your generation update. Could probably fit a lot more cells using that logic…

That’s what has been done. Every generation is on a single clocks edge.

Field Programmable Photonic Arrays are now “a thing”, so just imagine how fast GOL would run on those devices!

This seems dangerous. The one thing we know about evolution is that it loves time and, as simple as the starting point may be, it is unethical to potentially create life in this way. What if a dangerous AI emerges from this primordial soup?

Wait, what?

That person doesn’t know what they are talking about.

Or trolling

“Every frame includes pixels from over a million generations creating this beautiful pattern on the screen.”

You quoted the article wrong and introduced a factual error.

This breathy exclaimation also seems to imply a lack of understanding. “Even running at 60 frames per second it’s almost as fast as the monitor can handle.”

That’s because it’s running at 60Hz intentionally so that the monitor can handle it.