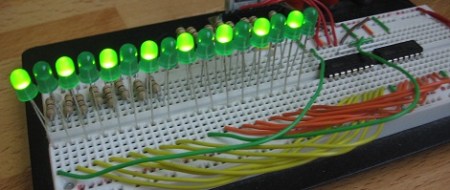

Hack a Day’s very own (and very prolific contributor) [Mike Szczys] put up a great tutorial on how to drive shift registers with an SPI interface.

[Mike]’s earlier tutorial of the 595 shift register goes through the functions of a shift register pin by pin. In a 595, bits for each position in the register are sent over one at a time. Most microprocessors have an Serial Peripheral Interface, and using an SPI bus means a lot less mucking about.

An ATmega168 was used for this build, although most Atmel chips can be made to work as an SPI master device. There are just three wires connecting the microcontroller to the shift register – SER, SRCLK, and RCLK. Like any other shift register setup, the build can be expanded by connecting the QH’ pin of the first 595 to the SER pin of the second.

[Mike] graciously made all the code for his build available. The video after the break is a 16-bit binary counter, a good stopping point before [Mike] rebuilds his Larson scanner/Cylon/Kitt, moving away from a PWM-based build to a register-based one.

[youtube=http://www.youtube.com/watch?&v=_goH3VUTHvI]

Some friends and I built an art project using 196 shift registers to drive 343 stepper motors.

It lived in the Science Museum of MN and the Exploratorium for a while:

https://picasaweb.google.com/116506934311171147250/AfterHours

https://picasaweb.google.com/116506934311171147250/Museum

http://bobodyne.com/web-docs/robots/Hex/index.html

I Live in MN also the Science Museum isn’t that great but I guess it’s fun for the kids!

Building up the suspense to E5F… you leave the audience on the edges of their seats… Masterful! (:

Ha! I figured it was such a boring video to watch that nobody would make it that far… you sir have proven me wrong.

You do make me think that I should have included a warning about over-current on the 595 chips if you light up more than 4 of these LEDs at once. I think the VCC pin is limited to 70 mA.

Nah…. you got to learn some things on your own.

The way I see it, once they find out the hard way, it’s something will remember, always.

If you just told them, they would soon forget.

Think about MIC5891 to replace your 595 ;-)

Anyone attempting a project should read the comments anywho :) so… basically you just did!

Isn’t that kind of the definition of SPI? Controlling arbitrary devices as shift registers?

Usually there’s some kind of addressing that goes on and a shared data line, no? I assume this tutorial walks you thru all that but I haven’t looked. Maybe there’s a dedicated /E per device in SPI. *shrug*

*unshrug* dammit, now I have to look.

Hmm… there seem to be a lot of issues with driving color displays (VGA and/or Composite) with these guys — I wonder with 2 or 3 595s and 3 (5 or 8 bit) R2R ladders if higher res vga (or other software generated video signals) could be realized. — Is the SPI faster than the core execution speed? (I think AVR can get 1 MIPS per 1 MHz… so the answer is probably no…)

What kind of speed does this pull compared to direct port access?

In my opinion you are not right. Write to me in PM, we will talk.

:)