[Jeri] has had a bear of a time moving up to Valve Software, but electron microscope is safely in her garage (!) and her electronics lab is slowly taking shape. Since she can’t bring out the real-life gravity gun she’s working on, she decided to show off a one-bit ADC that uses just a flip-flop to sample an analog waveform into digital data.

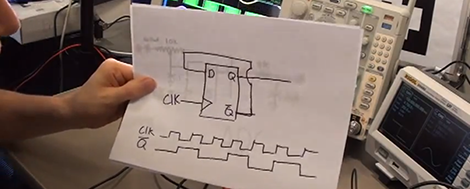

By toggling the clock input of a 74xx74 (or any flip-flop, really) and feeding the complimentary output to back into the data input, [Jeri] can get an output that is a 50% duty cycle feeding into the input of the chip. Adding an audio input to this data input with 10k pot to this feedback loop will cause the duty cycle to change in relation to the analog input, making a one-bit ADC.

As with any electronic shortcut, there are a few drawbacks: the clock cycle feeding into the flip-flop has to be pretty fast; at least a few dozen kilohertz if you’re sampling audio. Still, if you don’t have a free ADC pin, or you’d just like to build a bitcrushing guitar pedal, it’s a very simple (and cheap) way to get analog into a digital micro.

[youtube=https://www.youtube.com/watch?v=DTCtx9eNHXE&w=470]

since when is a few dozen khz ‘pretty fast’ ?

It’s a lot faster than I can strike something with my fingers (or hammer for that matter).

nice :D

what does valve need with an electrical engineer?

I wish I knew.

FOR SCIENCE!

REAL LIFE PORTAL GUN WOOHOO!

Wikipedia has the following link: http://www.valvetime.net/threads/im-working-at-valve-on-nextgen-gaming-hardware-jeri-ellsworth.187331/

Logically? A Valve “PC” console :)

My guess (best guess) is that valve & ID sofwtare are making VIRTUAL REALITY glasses “Oculus rift” I know john carmack is working close with the team, and that Gabe Newell is VERY interested in this concept and future of gaming

Can’t wait until that display starts selling.

Wow, where was Jeri when I was single! Electron microscope in the shed, as you do! She should be a pinup for all us geeky guys and a role model for every girl.

Yep, Jerry is groovy :-)

Damn, just wiki searched: she was so much better at everything then, than I am now: and I’m old enough to be her father (well, not quite, but humbled non-the-less).

Very good. Now feed it into an unmodified floppy drive and see what you get out.

That’s a really lovely scope to have at home by the way. Wish I could afford something like that.

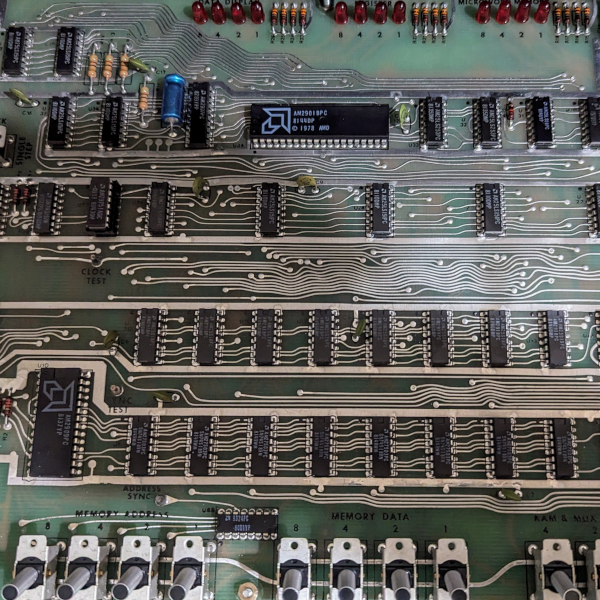

This is pretty timely as I spent a few hours last night learning about pwm clock manipulation and came across a lot of talk about the 74– series rocking it.

Ellsworth recently dumped a million hours of raw unedited video footage to YT of all her experiments and collaborations in the recent past.

I like her no-nonsense, practical way of explaining stuff on the back of a sheet of paper.

I agree, however I don’t like that her videos absolutely flooded my recently-added list in youtube, pushing all the videos I wanted to watch off in to the void >:(

Why would you want to watch anything else where there is so much Jeri & Friends!

It’s like Nerd Meditation, flick on an hour long video, sit back, and absorb the science.

We did something similar in Electronics engineering school. Only thing we did differently was use a digital 10k 256 step Potentiometer, which auto adjusted to get us as close to the curve of the analog signal as possible.

We were able to cleanly convert an 80k sine wave into 1 bit ADC and back again.

Same circuit, except we used a 10k digi pot and a few other little bits to adjust the pot up and down, depending on position in wave.

When CD players were introduced they started with many bit DACs but then moved to 1-bit DAC after a while, claiming superior performance.

Seems some things are reinvented a lot.

Superior performance = lots cheaper than a pair of 16 bit DACs running at the frequency required to convert the digital audio stream to analog.

The first consumer market CD player from SONY used a single 16 bit DAC and interleaved the channel decoding without using buffer and hold RAM. That made the channels a few microseconds out of sync. The first consumer market CD player from Phillips only had a 14 bit DAC and used interpolation to attempt to reconstruct the data from the disc it couldn’t process.

1 bit DACs run the clock extra fast and if they’re using a single channel DAC and interleaving for stereo they need a bit of buffer and hold RAM to synchronize the output.

1 bit DAC = CHEAP KLUDGE to make CD players cost less to produce.

That’s why I chose ‘claimed’, because to my mind 16bit seems better too, but hey a SATA connector is better than a parallel line too so what seems to make sense doesn’t always make sense and and with many things they replaced multiple lines with very fast serial with great success exceeding the capabilities greatly.

a one bit dac is not just cheap cludge, it is a great way to make a DAC that is inherently linear because it only has bit, instead of 16bits that need to be matched

And the oversampling greatly reduces the demand for an extreme reconstruction filter

half sample period delay at 44.1kHz is ~3.5mm at the speed of sound …

Now feed it a stereo audio signal and get a stereo signal back out, using the same minimalistic setup(plus some extra parts) and then I’ll be impressed ;)

1-bit ADC, meet 1-bit DAC:

http://www.fpga4fun.com/PWM_DAC.html

Here a falstad trying simulation 1 bit adc circuit

http://youtu.be/wK8_LAi6D_o

Cool circuit, but it’s not an ADC.

Analog voltage level in, analog duty cycle out.

Not delta sigma either.

Useful if you wanted to modulate a duty cycle with an analog voltage.

it is an ADC, the output of the flipflop is digital you just need to digitally lowpass filter and decimate to get a multibit output, that is how a delta-sigma converter works. The RC filter on the output does the same so you can see it on a scope it is in effect a simple DAC.

And yes it is delta sigma, the sum of input and feedback gets integrated(*) on the cap

(*) RC lowpass filter, only an approximation of integration

Perhaps I’m getting confused, but isn’t altering the duty cycle PWM? Doesn’t delta-sigma conversion use a fixed pulse width but alters the time between pulses?

you could say delta-sigma is a form of pulse width modulation, but they are not the same.

in short PWM is generally a fixed frequency of pulses with a variable width, delta-sigma is more of a “chaotic” stream of pulse with variable frequency and variable width

It’s kind of a to-may-to/to-mah-to thing..

A standalone delta-sigma is really just a voltage to frequency converter that runs a whole lot faster than the wave it samples. When the input voltage is high, the VFC flips between high and low really fast; when the input voltage is low the VFC toggles at a lower rate. Then there’s a counter that records the number of transitions in one sampling period.

You can also build a delta-sigma with a capacitor that charges to a known voltage at the start of every cycle, a comparator that decides whether the cap voltage is higher or lower than the input voltage, and a clock that counts the number of ticks between ‘comparator goes high’ and ‘comparator goes low’. Thing is, the output of the comparator itself is just a PWM’d version of the input. The ‘ADC’ part happens by taking digital samples of the PWM waveform at a much higher clock rate.

That’s pretty much what Jeri’s circuit would do if you connected it to a digital input of a microcontroller. Technically the circuit she shows in the video is just the PWM part, but it’s also the most interesting part.

No, that’s not quite right. With delta sigma, the pulses are fixed width, just that some of them are missing. You count the ones you see over a specific time period to work out that the input voltage was.

This is slightly different though. As well as missing the high parts of the cycle, you also get an equal number of missing low parts of the cycle too, so you couldn’t just count the pulses to work out what the voltage is.

I wouldn’t say delta-sigma is fixed with, yes they are always in chucks of whole clock cycles, but so is pwm, but if you look at the output ignoring the clock it can be high and low for any period of time

what you describe is a single slope ADC, it is not quite the same as delta-sigma

True enough.. a standalone delta-sigma uses pulse frequency modulation instead of pulse width modulation. PFM and PWM are related when you look at the time and frequency domains though..

Darn it, now I have to think about this. ;-)

A stock delta-sigma pulls a fixed amount of energy into (or out of) the input integrating cap whenever the cap voltage equals the input voltage. That’s the ‘delta’.

The time it takes for the input to replace the delta energy sets the frequency of the pulse train. The ‘sigma’ is a counter that adds up the number of pulses per sampling interval.

The key point is that the frequency of the pulse train has to be proportional to the input voltage.

The sequence of samples pulled from a continuous-time integral is indistinguishable from the discrete-time sum of a pulse train. You just have to scale the impulses so they represent the energy of the continuous time sample.

If the pulses are all the same size, the sum of the pulses is identical to a sequence of samples from the continuous-time integral of a constant.

Changing the frequency of the pulse train is equivalent to sampling the continuous-time intgegral at a different rate. That, in turn, is equivalent to sampling at a constant rate and scaling the width of the integral. Sampling twice as fast is equivalent to making the integral twice as wide.

In this case, flipping the target between high and low threshold voltages would have the same effect as pumping a delta into the integrating cap. Sampling the constant output from the flip flop gives you a pulse train, and changing the width of the pulse is equivalent to changing the frequency of the pulse train.

Yeah, there are obvious differences, but I’d have to say the math is close enough to call this a delta-sigma in casual conversation.

what makes a delta-sigma converter special is that it is noiseshaping, if you write out the transfer functions you’ll see that the input signal is just delayed, where as the quantization error is high pass filtered so it is easier removed by the following lowpass filter

Valve Software? do you mean to say that you are working for the game maker?

ok why would a game maker need a adc?

unless you want to make a rapid fire button by wiring into the fire button on the gaming device/mouse/keyboard or a quick zoom by wiring into the scroll wheel of the mouse.

rapid fire is nice for games where you have to earn fully automatic weapons or they are only given to players with high rankings or go down really long ladders quickly in tombraider.

Valve is a weird company, in a very very good way. There aren’t really “managers” there, exactly, so you can do pretty much what you want. I’m guessing it’s peer reviewed now and then and probably a little less free than I make it sound (based only on what I’ve read.) But a lot of their software products began as some random programmer’s whim and other employees jump on / jump off of the “project” as interest waxes and wanes. Best of all, their system appears to work VERY well.

the input of that flipflop will be forced to sit right in the “illegal” area where it is just between high and low, some logic families can get quite hot when you do that

That’s true for the older logic families, but she says at the start she’s using a chip from the LV family.

A quick check of the datasheet for the NXP 74LVC74As I use shows that my chips have Schmitt-trigger inputs specifically to avoid that problem, and all the other problems associated with slow-moving inputs.

I looked at the nxp 74LVC74A datasheet, and while it does say it has Schmitt-trigger inputs it does not list a hysteresis, but it does say max 10ns/V edge rate, and over temperature up to 5mA extra current for each input in the “illegal” area

and for this application hysteresis is bad

I’m guessing the 10ns/V you mention comes from section 8, table 6 (recommended operating conditions).. that’s the only place I see that particular number. ROCs are exactly that: recommendations on how to get the best performance from the chip, not limiting values. That specific value is the recommendation for higher voltages (Vcc = 2.7v to 3.6v). For lower voltages (1.2v to 2.7v) the recommendation is for slower transitions (20ns/V).

The hysteresis isn’t listed directly, but does show up in the specs for VIH and VIL (section 9, table 7). at Vcc = 1.2v, the hysteresis equals the supply voltage. The input voltage has to be at least Vcc to trigger a HIGH transition and at most 0v to trigger a LOW transition. For Vcc=2.7 to 3.6v, you have to go above 2.0v to get a HIGH transition and below .08v to get a LOW transition. In both cases, you assume a maximum hysteresis of 1.2v.

Re: the 5mA of overcurrent, the closest thing I see to that is dICC, and the 5000uA figure there is the guaranteed maximum for chips working at 125 degrees C. The nominal value for chips working at room temperature is 5uA, with a maximum of 500uA.

Re: hysteresis being bad in this application, I flat-out don’t understand what you mean. Schmitt triggers don’t have a forbidden band of input voltages specifically because of their input hysteresis.

The energy losses for chips that do have a forbidden band of inputs (the 74*04, for instance) come from shoot-through when the output’s pull-up network and pull-down network are both conducting at the same time. Schmitt triggers prevent that because their positive feedback forces fast transitions between high and low at the output.

For the 74LVC74A, you have to dig around to find the details, but the output rise and fall times are rated to be 15ns when Vcc=1.2v, and less than 6ns (nominal 2-3ns) when Vcc>=2.7v.

Vih and Vil doesn’t spec the hysteresis, they are value guaranteed to be seen as high/low

with hysteresis Vih would be different for inputs going high and being high

and hysteresis is bad in this application because it doesn’t work very well if the hysteresis is large compared to input signal

A Schmitt trigger has no high-going threshold when the output is already high.. all it has is a threshold that will make the output go low. Likewise, it has no low-going threshold when the output is already low.. all it has is a threshold that will make the output go high.

Let’s walk through it one step at a time:

– If we start with the input at 1v, there’s no way of knowing what the output will be.

– If we take the input to 0v, we cross the low-going threshold and the output goes low.

– If we raise the input back to 1v, the output will stay low because we haven’t crossed the high-going threshold.

– If we take the input back to zero again, we cross the low-going threshold, but it doesn’t do anything to the output because the output is already low.

– If we take the voltage to 3v, we cross the high-going threshold and the output goes high.

– If we take the input back to 1v again, the output will stay high because we haven’t crossed the low-going threshold.

– If we take the input back to 3v again, we cross the high-going threshold but it doesn’t do anything to the output because the output is already high.

Schmitt triggers don’t go into an indeterminate state for input voltages between the high-going and low-going thresholds. They stay in whatever state they’re already in. The fact that their output is a function of the input *and* the output is input hysteresis.

Take a look at a 74*14 (hex Schmitt inverter) datasheet and look at the threshold voltages. You’ll find there are two, named Vt+ and Vt-. The hysteresis is Vt+ – Vt-.

same thing different words, with hysteresis Vih_min is different for an input that is high than it is for an input that is low , in your example 1V vs. 3V

74*14 has Schmitt trigger inputs and specify the hysteresis, 74LVC74A doesn’t specify what the hysteresis is, there is some there always is but the datasheet doesn’t say

The levels make no odds really, it’s the tsu and thold that are being royally violated. Still, if it works…

when sampling an async input with a flipflop you always run the risk of violating setup or hold

just means you might get a delay of one cycle or the tiny risk you hit metastability which will generally resolve very fast in modern logic

It’s not a digital circuit where you need a zero bit error rate or the function it performs will fail it’s specifications.

It’s an analog circuit where errors only will be accounted as increased noise or distortion on the sampled output.

Knowing it’s limitations, the only issue with the lack of a proper input comparator is the increased power comsumption.

Isn’t a “1-bit ADC” just a comparator/overdiven opamp?

What an odd thing to say.

This is not Sigma Delta !!!

it is just a PWM converter

No discussion of oversampling and the choice of a clock frequency. No discussion of choosing optimal filter characteristics. A very incomplete presentation. I wonder if that is due to lack of knowledge or lack of attention to detail. Either way it doesn’t look good.

The circuit is even named incorrectly. By strict definition, this is not a delta-sigma converter, it is a pulse width modulator. The use of a flip flop in the application can be troublesome for different reasons whether the input has hysteresis or not. That’s already been discussed here. Purpose-designed comparators exist for a reason.

I wonder where this person earned her EE degree…

sure there’s lots of details missing but it is hack to illustrate a concept, not a production ready circuit.

And by what strict definition is this not a close approximation to first order delta-sigma modulator ?

input plus -output (delta), integrated on capacitor (sigma)

it is RC and not true integration but ..

May be you could show us your videos where are sharing all that knowledge we are missing? Thanks.

http://www.youtube.com/v/MfFh5v0DH-Y

Analog to PWM? This might be useful for when I build my RGB LED panel. I could connect 3 of these to the blanking inputs of MAX6969s, add some anode transistors and refresh the display with a traditional raster scan pattern.