It’s a well-known conundrum that while most computers these days are digital in nature, almost nothing in nature is. Most things we encounter in the real world, whether it’s temperature, time, sound, pressure, or any other measurable phenomenon comes to us in analog form. To convert these signals to something understandable by a digital converter we need an analog-to-digital converter or ADC, and [Igor] has built a unique one from scratch called a delta sigma converter.

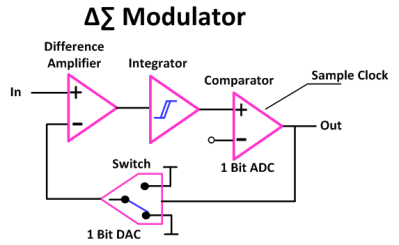

What separates delta sigma converters apart is their high sampling rate combined with a clever way of averaging the measurements to get a very precise final value. In [Igor]’s version this average is provided by an op-amp that integrates the input signal and a feedback signal, allowing for an extremely precise digital value to be outputted at the end of the conversion process. [Igor] has built this one from scratch as well, and is using it to interface a magnetic rotary encoder to control digital audio playback.

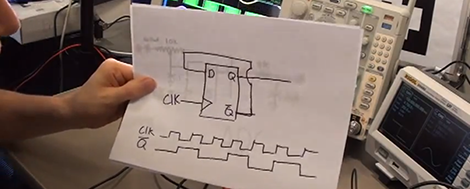

Although he has this set up with specific hardware, he has enough detail in his video (including timing diagrams and explanations of all of the theory behind these circuits) for anyone else to build one of these for other means, and it should be easily adaptable for plenty of uses. There are plenty of different ADC topologies too, and we saw many different ones a few years ago during our op-amp challenge.