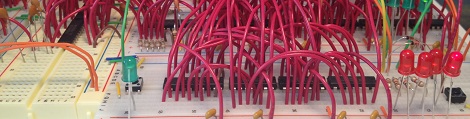

If you’re going to build your own computer, it probably wouldn’t do you well to exactly emulate the computer you’re looking at right now. The modern x86 and x64 chips that power your desktop or laptop contain hundreds of individual instructions, and the supposed RISC CPUs found in ARM-powered devices contain nearly as many. No, if you’re going to build your own computer you should make it easy on yourself, just as [Jack Eisenmann] did when he built the DUO Compact, a one-instruction set computer made on a breadboard.

Instead of dozens or hundreds of individual instructions, a one instruction computer has – like its name implies – only one way of manipulating bits. For the DUO Compact, [Jack] chose a NOR and fork conditionally instruction. Each line of assembly written for the DUO Compact has four memory instructions: a source address, destination address, skip address 1, and skip address 2. [Jack] explains exactly how this operation can allow him to compute everything:

Three steps occur when executing the instruction:

- Load the byte at the first and second address. NOR these bytes together.

- Store the result of step 1 in the second address.

- If the result of step 1 was zero, then skip to the instruction at the fourth address; otherwise, skip to the instruction at the third address.

As if designing a one instruction computer built using only basic logic and memory chips wasn’t impressive enough, [Jack] went as far as writing an emulator for his system, a compiler, an operating system, and even a few programs such as a square root calculator and a text-based adventure game.

By any measure, [Jack] has finished an amazing build, but we’re blown away by the sheer amount of documentation he’s made available. He’s even gone so far as to write a tutorial for building your own DUO Compact.

You can check out a few videos of the DUO Compact after the break. Of course, if you’re looking for a project to tackle, you’re more than welcome to design a PCB from the DUO Compact schematic. We’d certainly buy one.

[youtube=http://www.youtube.com/watch?v=IoMgCrOT3fU&w=470]

[youtube=http://www.youtube.com/watch?v=rqaZvJXc1Fk&w=470]

The thing nightmares are made of :

Come back to your desk after an argument with your roommate to find a single jumper laying on the table.

I’ve been there before…

Sounds like my Digital Logic Instructor’s tests (after building the ALU, now troubleshoot it)

Reduced in RISC refers to the instructions themselves rather than the size of the instruction set.

Not sure you’re correct on that. Having been around computers for a few decades now and remembering all of the hype when RISC (Reduced Instruction Set Computing) architecture came on the scene, the big deal was that the chips were simplified and therefor faster because they had FEWER instructions in their instruction set, not that their instructions were less complex.

Incorrect:

http://en.wikipedia.org/wiki/Reduced_instruction_set_computing

This design wouldn’t make use of a (normal) program counter, since you always perform a JMP after every NOR. I think that, if you did use a PC, you could get away with only three addresses per command. The fourth address is inferred as the current address + 3. This is very similar to the SUBLEQ OISC described on the Wikipedia entry for these types of processors: http://en.wikipedia.org/wiki/One_instruction_set_computer.

Cool stuff and a nice build :)

Nah, it’s good the way it is. Now you can choose between a relative or absolute jumps in the same instruction. Hell, with this design, there might even be a way to use the memory ports to allow for it to use an sd card reader.

All and all though, this is a hell of an excellent project. I can’t wait to see it off its breadboard and soldered to a PCB.

Yep, the current design is more flexible and would make it a bit easier on the developer. Though who are we kidding, developing in ASM for this thing would be awful ;) Some sort of macro assembler would make things a lot more bearable.

Fuck yeah man.

I love seeing stuff like this. That looks incredibly time (and brain) intensive!

Very cool… I’ve followed his other builds too. There’s some very innovative stuff he’s done. Inspiring!

How fast does it run?

How many instructions does it have to run typically to emulate a “regular” instruction?

How about a massively parallel multicore processor built from this design? I wonder how many cores you could fit on a modern FPGA? All working in the same memory space.

Hmmm, CPU after next from AMD or Intel, only has one instruction but runs at one Yhz, that’s Yottahertz.

Why is it called DUO when it has only one instruction? Shouldn’t it be UNO?

This should def be rebuilt in an FPGA. then crank the clock speed way up :-)

So, does modifying this computer by adding an additional instruction count as one-upmanship? :)

when I first saw the headline, I wondered what that one instruction might be. a NOP is pretty easy to implement ;-)

nice project, though…

I remember hearing about “theoretical possibility” of a 1ISC, it is nice to see an actual implementation.

The Chuck Norris computer language, just one instruction: Do it.

Al Williams built a 32 bit OISC on an FPGA back in 2009.

http://www.drdobbs.com/embedded-systems/the-one-instruction-wonder/221800122?pgno=1