There have been quite a few boards put out in recent months with an FPGA, some RAM, Flash, and a bunch of I/O, the working theory being FPGAs are the new hotness, ready to steal the crown from Arduino and put a programmable logic development board in the hands of millions. We’re not so sure that’s going to happen. but Scarab Hardware’s miniSpartan6+ board does look pretty nice, and has more than enough on board to serve as anyone’s first FPGA platform. It’s also one of the first FPGA boards we’ve seen that is breadboard friendly. Nice touch.

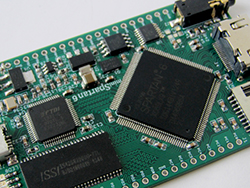

This tiny board features a Spartan6 LX9 FPGA, with just under 10,000 logic cells. An FPGA platform is useless without some sort of IDE, so the Scarab Hardware folks have taken the Mojo IDE, improved the GUI, added a few libraries, and rolled everything up into a ‘not the Arduino IDE, but as simple and better’ platform.

Right now, the crowdfunding campaign for the miniSpartan6+ is well over 200% funded with a little less than a month to go. The stretch goals the team have in mind – a very likely probability, given what they’re asking – include a faster FPGA, a higher resolution ADC, and support for HDMI input and output. That last bit – HDMI input – will allow anyone to do some cool things like overlaying video with HDMI for a pretty reasonable cost.

I went for it. This is the perfect excuse for me to get into the FPGA world.

Check numatolabs, they have dirt cheap FPGAs, offers academic discounts. A spartan 6 board with no RAM will cost you around 35$ there

Thanks Ayush!

DE0-Nano from Terasic is the best FPGA for starters. It includes an onboard ADC, Accelerometer, 32MB SDRAM, 2Kb I2C EEPROM etc and is priced at 59$ (academic).

The issue isn’t the price but the ecoystem around the plattform.

There are several rather cheap FPGA and CPLD boards.

TI’s launchpads and MSP430 MCUs are also cheaper than the Arduino Boards but their libraries, IDE and learning ressources are just horrible compared to the ease of use of the Arduino ecosystem.

If they can deliver what they promise this is going to be an awesome plattform, while this can in no way compete with the Arduino because of the complex HDL languages (hopefully that changes aswell with PSHDL) this can finally be an rather easy way to get into the FPGA world. What that is missing is a simple headache free IDE, lots of good easy to use libraries and super simple tutorials for bloody beginners in the FPGA realm.

I’m interested to see the Scarab IDE. I missed this kickstarter campaign by less than an hour. :((( I do, however, have a sexy FPGA platform — the Pipistrello… “a Papillio on steroids” — with a Xilinx Spartan 6 LX45-3 and a single HDMI port, among other peripherals.

I’ll be very interested to see if the Scarab IDE can help me pull off some stuff with this FPGA kit that I would have a very hard time figuring out on my own. When the Scarab FPGA kits go on sale post-Kickstarter, I’ll be very interested, if for no other reason than having the opportunity to play with an HDMI input AND output on the same board. For now, I’ll just try to see if I can bone up on HDL the hard way while I wait to see what Scarab can put out there.

The only way to unseat the arduino is to make it as easy to program with a metric buttload of USEABLE libraries.

TI failed with their MSP430 because their libraries are a utter mess, and their IDE is a bigger mess. FPGA’s are significantly harder to program, so you will not see grade schoolers programming them in an intro to electronics class liek you see them do with Arduinos and rasPi’s.

The only thing is that TI does not target the MSP430 line to the hobby market as much as the Arduino platform does. You could argue that they have several Launchpads, but I have seen them being used mainly by universities. Also, for what is worth, I consider Code Composer Studio to be miles ahead of anything the Arduino IDE can even dream to provide.

Back when I started walking this path, I found the Arduino IDE too limiting and within a week, I was using something else (Eclipse with the AVR plugin). I found the Arduino libraries too buggy and slow, so within another week, I was writing my own software using avr-libc. After a while I found the Arduino form factor to be too inefficient, so I started making boards of my own. I then started looking at other platforms and encountered the MSP430. I really like what the Launchpad did by adding the eZ430 programming and debugging interface onboard.

If there is something I do not like about TI, however, is their documentation. It is not lacking, it is too abundant, so abundant that it is easy to get lost within it. TI writes their documentation as if they were Bibles. It is very easy to miss the small details on how to make something work.

Most will put a soft CPU on it… and boot uClinux… ;-P

The MSP430 did have low unit cost, but nowhere near the AVR in volume. TI’s uC stuff is not really production design ready, but it’s problems are almost all caused by the old Stellaris “cursed code” business models.

Personally, I’d rather take any old 8052 or even shitty pre-gcc Microchip compilers, because at least their stuff works reliably. Now days, the open Pi GPU on the ARM1176JZF smokes a FFT, and the Debian repo with gcc essentially dwarfs most options. I’ve also tried Altera NIOS II dev kits that are about the same price as the above Spartan6 project, but like all FPGA projects you get jacked for working library IP and spend your dev time wrestling with a proprietary board support package.

You say to us : “Most will put a soft CPU on it… and boot uClinux… ;-P”

Sorry, I want my quadcopter to fly… In real time applications, assembly code is the best option.

Altera NIOS II, is a great thing, very cheap and with great support

Just about any $3 mcu chip can do a flight controller quite nicely.

If you need more… you are doing it wrong…

An FPGA also has some other design considerations, and if you work with them for awhile you’d understand why its a bad idea.

“In real time applications, assembly code is the best option.”

In case anyone has the misfortune of being too ignorant to identify this as FUD: it’s FUD.

This is the same mindset which makes people buy .45 ACP for a concealed carry firearm(that they never wear because it’s too big and heavy) or a giant SUV for their 15 commute on the express way because they are delusional enough to believe they might be able to amortize the mpg premium by saving $300 on rental fees for their bi-annual camping trip.

OpenglMan is obviously an engineering student(or troll) parroting their professor wax nostalgic for the “glory days” when driving cost out of their BoM was worth wanking through hundreds of hours of NRE expense writing hex values with a magnetized needle.

If you make $2/hour in china making $10 studfinders for dealextreme this logic might fly.

If you are making <1000 of something,and have a reasonable power budget(can afford the extra 100mA) then do yourself a favor and view this level of absurd lack of pragmatism for what it is:

A factually incorrect impression of experience(of a relic from the past) masquerading as demanding requirements. IE: Necessitating difficult sounding billable hours and hand-waving to excuse being behind schedule and over budget.

Hugs and kisses from a whippersnapper that isn't so wet behind the ears to buy this bullshit.

WARNING: Emulate antiques verbatim at your own peril.

-$10 on the BoM makes your 3 months of labor irrelevant.

-Stay current with your skills or perish.

That is totally true. You need the family datasheet, the chip datasheet, the package datasheet, the UART datasheet, the ADC datasheet, the PWM datasheet… usually 200 pages each.

Also, I like the Code Composer Studio only after I’ve got the project set up. Setting up your first project can be Kafka-esque.

A few of the ARM chips documentations are even worse than TI’s MSP430 multiply by the complexity of the peripherals.

I was reading Freescale datasheet and not even sure if sections of it is applicable to the specific chip I am using nor does anywhere it states what exactly features I am getting. e.g. Trying to find out what pins are 5V tolerant was fun as the datasheet implies there should be some as there is some numbers in the electrical specs, but don’t name the actual pins. Their product briefs (which normally not what I would use) on the other hand said that it is not even supported in that family.

Let us not forget Energia for an IDE that is “Arduino like”, works great, and allows you to take a lot of native Arduino code and just cut ‘n paste. Energia doesn’t get nearly the props it deserves IMHO. If u need more oomph then you’ve got Code Composer.

Looks like there’s just one HDMI port so it’s either input or output, but not both like on the NETV.

We would like to thank everyone who baked us and Brian Benchoff for his nice article about miniSpartan6+

@Doc Oct

We are updating our circuit and it will include 2 HDMI Ports, please check Update #4 on the campaign.

Thanks

Why would someone *need* to match length on the FTDI chip to Spartan 6!? (right above the baord name silkscreen)

The SDRAM doesn’t need tracks either, but I can understand. Might also need to space out to have a track between the LED & resistors. Probably longer than 10 mils of tracks for the solder resist coating.

Not sure if the HDMI would require some kind of licensing fees etc.

^ track matching.

Thanks a lot for your comment.

We did match the length of the traces going between the FTDI chip to Spartan 6 because the FTDI chip can be used to transfer 480Mbps, according to the datasheet of FT2232H. Also the datasheet mentioned that the port we are using is supporting 40Mbytes/sec.

When we design the board, we didn’t know if we are going to use that high speed or not so we matched the length just in case.

You are correct about the LEDs. We had a wrong footprint and we ordered larger footprint. The board in the picture is assembled by hand so it was not a problem but we are going to fix it in the final layout. Good catch!!!

I am not sure too about the HDMI licensing fee but we will check.

Thanks again for your comment and we would like to hear back from you if you have any suggestions.

FT2232 has a 8-bit parallel FIFO interface. I am assuming that’s what you are using.

Signal propagation on a PCB is about 1/2 feet per ns. You data rate is once every 25ns… So even 1/2″ of track difference is like 1/3 of a percent.

I would question the “just in case” part or not being able to look at the order of magnitude of a simple timing requirement.

cut them some slack… perfectionism never hurt anyone

You realize that what you said is ironic…

It is not good be to a perfectionist if I happen to expect the designer to know when something is actually needed (the “when” and “why” part) and when it is not. To me, doing something without a good engineering reason (“when” and “why”) is a sign of lack of experience and confidence. (The “how” part is not why I am talking about it.)

The same board space could have been used for the much needed decoupling caps. Typically FPGA vendors recommend a cap *per* power pin as they don’t know how their chip is being used, but in reality you can get by a factor of 1/2- 1/3 or less etc depnding on what you are doing. I wouldn’t do it with that little amount of caps especially the chip is driving a lot of I/O to the SDRAM (Simultaneous switching). That layout looks like 1 per I/O bank.

Also a lot of FPGA noobs would be hooking up their boards and not knowing that the I/O are not 5V tolerant…

That’s a fair point especially given that we can only view the gerbers of the back and no pictures (can’t seem to see sm0603 footprints…)

short answer: they don’t need to be matched. the sdram also doesn’t need to be length matched. the traces are so short it doesn’t matter (under 1.5 inches). Been there, done that.

More likely the lengths were matched because the guy doing layout had a lot of spare time and had nothing else to do.

They don’t hurt anything, but they are tedious to add (especially in EAGLE which is a sad joke of a cad program)

More important is that they paid attention to return paths and have adequate grounding, which appears OK

One would only have to start worrying about that when the skews start going into double digits of percents on the eye opening.

Too few decoupling caps around the FPGA for confort.

http://www.hdmi.org/learningcenter/trademark_logo_pub.aspx

1. What are the Adopted Trademarks?

from the pdf: >2. The terms “HDMI” and “High‐Definition Multimedia Interface.”

2. When is use of the Adopted Trademarks prohibited?

from the pdf:

>1. No use by unauthorized parties

The Adopted Trademarks may be used only by authorized licensees who have entered into an Adopter Agreement with the HDMI® Licensing Agent, as well as their authorized distributors and resellers pursuant to the Adopter Agreement.

>2. No use with non-compliant or unlicensed products

Use the Adopted Trademarks only in connection with the promotion of the HDMI Specification, and on products that are fully compliant with the HDMI Specification.

So might want to talk to a lawyers first or not mention those are “HDMI” connectors. Call them a digital video interface or whatever.

Just call them “high speed differential I/O”. The fact that they can be used for HDMI is just a coincidence.

highspeed differential messaging interface?

Why not use the Xilinx IDE ?

Xilinx is not the greatest. It’s a 15Gb install and doesn’t support windows 8 (you can get it working on windows 8 but it needs some fiddling around). That said, Xilinx is pretty powerful and I hope their IDE provides at least as much useful functionality.

“The Scarab IDE only requires the Xilinix ISE Design Tool to be instlalled on your machine”, so you still have the 15Gb install and windows 8 issue.

Real programmers use Linux anyhow.

I’m not surprised someone named “Tux” would be so ignorant. Real programmers can program on any platform.

please but real programmers (at leat none of my co workers) friends / aquitances that produce code use win8… heck even our CFO hates it…

Real programmers watch porn, not terminal screens.

Especially when it requires the ISE to be installed… Xilinx’s “IDE” isn’t that bad and don’t need bloated installs on top of that.

the mojo ide actually calls xilinx planahead binary to do the real compilation work

Yes, so the big question is what you actually gain by another layer on top. I don’t think much is gained, but quite a bit is lost. Developing for FPGA is more than just writing some HDL and hitting “go”. It also involves simulation, constraints editing, and timing analysis, to name a few.

Yes, it looks good. But – is it $100 good? That’s the smallest Kickstarter funding still available.

Hey, you can get the kit for the $69 rate. That level is not limited.

Deal ! It’s actually $79 for those of us outside the USA but that is good enough for me…

That price is good if you are using the features on the board. There are a lot of other cheaper FPGA boards around if all you need is a generic FPGA board. See URL.

http://www.joelw.id.au/FPGA/CheapFPGADevelopmentBoards

(Note .AU domain Some of the prices are some of the prices are out of date.)

Anyone who thinks fpga’s are going to dethrone the arduino needs to have their head checked. Fpga’s have a much steeper learning curve that even long time electronics hoobyists have a hard time understanding. The arduino on the other hand offers an incredibly quick and easy way to make things that would be nearly impossible without years of experience. These two aren’t even in the same galaxy.

I love FPGAs, but I have to agree with you Mike. They are definitely more fiddly to use. Whenever people at work ask about using one I always suggest that if they can sneak the required functionality into a microprocessor (say a Texas Instruments C2000, they really are excellent) they should.

Where FPGAs start kicking arse and taking names are applications with:

1) strictly deterministic timing is required (and ‘about 1 microsecond’ is not good enough). Think radio, radar, power electronics, etc.

2) highly reconfigurable IO is required (modern FPGAs support like 20 IO standards).

3) weird custom comms standards are required.

4) there is lots of heavy fixed point numerical work that can be parallelised. Imagine 32 cores @ 100 MHz – this will beat the stuffing (if properly programmed and the task allows it) out of a 3.2 GHz processor because the FPGA can do many things simultaneously _all the time_. No waiting for cache missed, operating system calls, task sharing etc.

Also note: the Spartan 6 LX9 can be designed onto your board and hand soldered. (Lots of flux, nice clean chisel tip iron, use the ‘rolling ball’ soldering method, and a little bit of solder wick to clean up shorts). You’ll need a 4 layer board though.

I’ve made a few 2 layer boards with the Spartan 6 TQFP144 device and had no problems.

This looks like a nice board and the ide seems to simplify project setup compared to ISE. Still two point bother me :

– is it a 4 layer board ? While HDMI and sdram may work on a 2 layer board, the high speed io (stretch goal upgraded the FPGA to -3 speed grade) can be a problem.

– Kickstarter page mention a stereo vison camera … Please show the code and specs, epipolar rectification, stereo matching and depth map filtering usually require quite a bit of computing power and memory bandwidth to run real-time (at least 30fps) with good resolution (VGA).

One thing that stills bothers me is that there is no lightweight synthesis tool for VHDL or Verilog. You have to download those huge 6 GB in order to be able to simply use your board.

Also, even though HDLs are platform independent, you must use specific tools to develop for each target. I know this is required given the way each company implement its technology, but perhaps a standard tool could be created to synthesize for any target FPGA by the collaboration of different companies or by the adoption of a standard in ‘converting’ the bitstream to hardware.

I suppose that this would enhance the user experience and get more users involved with this technology.

Since there are only 2 major brands, and a few smaller ones, there’s little incentive to create a standard tool set. And even if there was incentive, it would be extremely hard, and would require proprietary information for all the FPGA hardware.

Altera Quartus II is just 1.5 GB. I use it to program Cyclone IV devices for which we need to add an additional package of 500 MB making it a total of 2GB setup. You get a DVD containing the setup and the Modelsim simulation tool if you purchase any board from Terasic.

“That last bit – HDMI input – will allow anyone to do some cool things like overlaying video with HDMI for a pretty reasonable cost.”

Sounds like the perfect all-in-one solution for homebrewed advanced Ambi-Light clones!

(Without needing the separate hdmi-to-svideo and svideo-video-capture hardware.)

Won’t work. You don’t decode the HDMI video to do the overlay. It’s still encrypted.

Weeelllllll, if you look closely at the code the cipher does actually run but Bunnie uses the result to encrypt a new pixel rather than decrypt the original one :-) It is a trivial task to swap the usage of the cipher but obviously Bunnie didn’t want to say it in quite those terms.

Am looking for a nice schematic or graphical entry GUI. Is there such a thing?

I don’t have time to learn vhdl or verilog

Almost all FPGA development tools have that option. With schematic design tools in the IDEs, you can use the FPGA specific IPs and form connections to realize your digital circuits. However, this approach fails when your design has way too many components involved. Take a look at this ftp://ftp.altera.com/up/pub/Tutorials/DE2/Digital_Logic/tut_quartus_intro_schem.pdf

My Xilinx FAE mentioned this board to me; been looking to get back into cheap Spartan projects instead of $10k Virtex projects. Excited to check it out and I appreciate the attention to detail the Scarab folks are putting in.

Hmmm, you folks ever heard of XESS.COM and his XULA2 Spartan 6 LX25 board? or LX9? LX9 at $69, LX25 at $119. LX25 can do a lot. My only gripe with his modules (I have an LX25) is the SINGLE GROUND PIN. All off-module signals will likely have crap for signal integrity because of this, but maybe the differential modes have a shot? Along with the baseboard XESS has, you can use Papilio I/O modules. On-board, there’s a MicroSD and hefty RAM chip, plus USB programming chip. I hardly hear XESS’s product mentioned, but it’s quite a bargain – the LX25 is just beginning to have enough memory to make a soft CPU core useful (on the order of a Arduino’s code size).

Sorry to dredge up and old topic, but my miniSpartan6+ arrived, and I’ve documented how to get started with it under Windows.

You can find it on the projects page at the Hamsterworks FPGA WIki, or click on the link above.

Search for Spartixed listed at kickstarter – the price is $29 for initial backers and $35 if you missed. It has Spartan 6 and is great for learners.