Look at any sufficiently advanced CNC machine or robot, and you’ll notice something peculiar. On one hand, you have a computer running a true operating system for higher-level processing, be it vision or speech recognition, or just connecting to the Internet. On the other hand, you have another computer responsible only for semi-real-time tasks, like moving motors, servos, and reading sensors and switches. You won’t be doing the heavy-lifting tasks with a microcontroller, and the Raspberry Pi is proof enough that real-time functions aren’t meant for a chip running Linux. There are many builds that would be best served with two processors, but that may be changing soon.

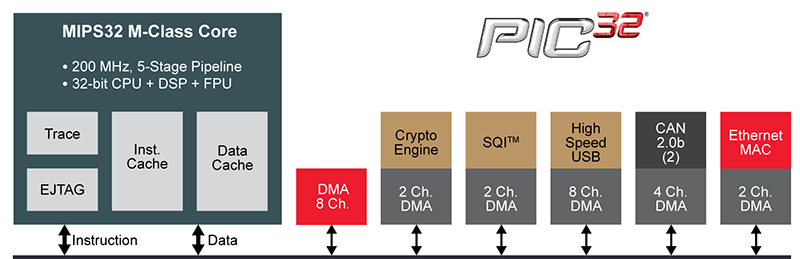

Microchip recently announced an addition to the PIC32 family of microcontrollers that will support hardware virtualization. This addition comes thanks to the MIPS M5150 Warrior-M processor, the first microcontroller to support hardware visualization.

For microprocessors, hardware virtualization has been around for a long time. The first experiments with hardware virtualization began in the IBM System/360 era, with hardware extensions to the x86 architecture showing up in Intel and AMD processors a decade ago. Microcontrollers and systems on a chip have not had hardware virtualization, and the new MIPS M5150 is the first microcontroller to offer the capability.

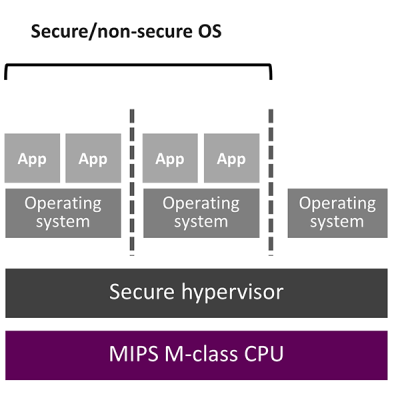

The virtalization of the MIPS M5150 is accomplished by a hypervisor provided by Seltech. On top of this hypervisor, a number of different operating systems, from real-time systems to pedestrian Linux apps can run concurrently, completely separated from each other.

The virtalization of the MIPS M5150 is accomplished by a hypervisor provided by Seltech. On top of this hypervisor, a number of different operating systems, from real-time systems to pedestrian Linux apps can run concurrently, completely separated from each other.

In a video from Imagination Technologies (available below), the true power of hardware virtualization on a microcontroller can be found. A MIPS M5150 CPU runs Linux and the uiTRON operating systems on the same CPU. The uiTRON system controls a motor, and the Linux boots and restarts, without affecting the real-time system. Try doing that with any of the dozens of ARM Linux boards out there.

While the PIC32 isn’t exactly an extraordinary powerful microcontroller – in terms of performance, it’s more akin to the SoC you would find in a router – the ability to run real-time systems alongside general purpose operating systems is a game changer. With hardware virtualization, applications ranging from smart robots, exceptionally capable quadcopters, and CNC controllers that actually make sense are possible.

Pru could also be used on sitara processors.

“the Raspberry Pi is proof enough that real-time functions aren’t meant for a chip running Linux”

Linux isn’t a RTOS. however ECos, FreeRTOS, RTLinux, RTEMS and few others are all open source RTOSes that can all run on the Raspberry Pi. this shill piece for Microchip is extremely transparent.

That’s right! HAD should never tell us about potentially useful things that are not open source plus ultra! I feel violated because they didn’t hate on it and were not flawless in all the copy.

Plancton’s Karen computer voice: “Strawman: 50% straw, 50% man!”

It’s not even a shill piece for Microchip, since it doesn’t get the product details right. It’s just a reprint of an ImgTec blog post that is either misinformed about the PIC32 chips, or does its best to insinuate they’ve got features they actually don’t. Either way, real HAD level reporting here.

Blog article author here: The post is talking about the new PIC32MZ EF MCUs which use a MIPS M-class CPU. This CPU is based on Release 5 which includes full hardware virtualization. The new Altair FourGee-1150/1160 processors use the same CPU and provide similar functionality, albeit for LTE modems.

Why don’t you go download the datasheet for the EF series, and see for yourself? Unless Microchip have chosen to keep all the virtualization information secret, it’s not there. The Config.AR bits are also documented as returning MIPS32r2 support only, and Config3.VZ isn’t even mentioned.

The datasheet clearly mentions a MIPS M-class CPU. Here are the specs for the M-class CPU family.

http://imgtec.com/mips/warrior/m-class-m51xx-core-family/

The M51xx cores implement the latest MIPS Release5 Architecture, incorporating hardware virtualization for increased security, IP protection and reliability for a wide range of applications including: industrial controllers, Internet of Things (IoT), wearables, wireless communications, automotive and storage.

Virtualization support is provided for both the microcontroller-class and embedded processor versions of the M51xx family, a feature not available in comparable alternatives.

Additional security is provided by the ‘anti-tamper’ feature in these cores, which includes countermeasures that provide resistance to unwanted access to the processor.

For some reason Microchip did not document ivirtualization but Config3.VZ=1 on this chip, according to my friend who tested it today

Indeed.

–“the ability to run real-time systems alongside general purpose operating systems is a game changer.”

It’s been a long time practice to run something like a Linux kernel as a process under a proper RTOS kernel. It’s basically what all timing critical systems do.

And hasn’t ARM had hardware virtualization (in the form of TrustZone) since at least v7? Iirc Geode OS does something quite similar to what you’re describing.

TrustZone is not hardware virtualization, it is a set of security extensions. They are different.

The blog article speaks of full hardware virtualization available in an MIPS MCU-class processor, a feature you will not find in any Cortex-M.

Yes, but it has never been virtualized before in a microcontroller. That is the whole point of the demo, to show you can run two or more operating systems on the same chip using full hardware virtualization and a hypervisor. By running these operating systems in isolated containers, one’s operation is not dependent on the other. In the case you are describing, if I shut down the RTOS, Linux goes down too. In our demo, shutting down one does not stop the other.

But that’s just the same thing. The RTOS == Hypervisor. You never shut it down.

That’s the way it’s been done everywhere from industrial automation to your wireless router. You have a minimal RTOS kernel that boots up first and shuts down last. The actual software is divided into a deterministic real time part which is scheduled a certain number of cycles by the RTOS kernel, and the rest of it goes to whatever user front-end OS you’re running, and the RTOS also serves memory management between the two so you can communicate from the userland to the real-time part.

The fact that you have a hardware hypervisor is basically… so what? You still need a whole RTOS running on one virtual machine, and the user OS on another, and now it’s just more complicated to pass messages between the two because the real time part doesn’t have direct access to the user OS’s memory.

In other words, in most real world applications, there isn’t any need for multiple isolated operating systems on one chip. They’re always more or less inter-operating, and thus don’t need to be virtualized into private virtual machines.

There are two types of hypervisors: type 1 (or native) hypervisors runs directly on the hardware (bare metal) while the guest software runs in the VMs. Microsoft Hyper-V is an example of a native hypervisor.

A type 2 (or hosted) hypervisor runs within a conventional operating system environment – this is what your are referring to.

On a MIPS CPU, a type 2 hypervisor (FEXEROX) runs in kernel mode while the guest operating systems (here Linux and iTRON) run in user mode. In this way, any access that the guest operating systems try to make to a privileged region of memory or execute a privileged instruction will cause an exception that is handled by the hypervisor running in kernel mode.

There are multiple use cases for this kind of operation. Let’s take automotive. You can have one body ECU that performs three basic functions: moves mirrors, unlocks the car, moves the windows up/down. Rather than put all these under the same RTOS or have them implemented on separate chips, you could virtualize each application in a single core on separate containers so if something happens to one, it does not affect the operation of the other two.

I can offer others if you want to learn more.

The PIC32MZ EF does not support virtualization. It has an M-class FPU, otherwise it is an microAptiv core.

The M-class refers to the MIPS CPU. There are three families of Warrior CPUs:

– P-class aimed at high performance application processors (e.g. P5600)

– I-class targeting mid-range mobile and embedded markets (e.g. I6400)

– M-class targeting microcontrollers (e.g. M5150 and M5100).

All the four CPUs mentioned above feature hardware virtualization. P5600 supports up to 15 guest operating systems, I6400 supports up to 31 and M5150 supports up to 7. Whereas at the high end you will see virtualization present in competing CPUs, the M-class is the only licensable MCU family that has this feature.

Hard realtime I/O? XMOS.

The datasheet for the PIC32MZ EF claims it has a full MMU with 16 TLBs. I may be misremembering but the MIPS architecture ala MIPS was already fully virtualizable. I don’t see any obvious reason this chip can’t.

The article is talking about the new hypervisor module that is a new extension to the MIPS32r5 architecture.

>the ability to run real-time systems alongside general purpose operating systems is a game changer

no its not, over complicating your design and locking it to one particular ventor/product just to save $5 on additional MCU? are you crazy??!?!11

plus you can go microchip, OR you can save yourself from gray hair and tens of hours lost on hunting undocumented hardware bugs by switching to ARM

ARM Cortex is hardly bug free though. Have you seen the list of hardware errata workarounds in kconfig?

“…the first microcontroller to offer the capability”

Define microcontroller first. My definition for escaping the micro-controller world is a MMU and thus the ability to run an HLOS. There are lots of high-end variants of Cortex M devices with more I/O and expand-ability than many low-end variants of Cortex-A devices – eg high end SAMV7x or STM32F7 verses low-end SAMA5 or Vybrid. Yet the formers are squarely in the “micro-controller” world and the laters are still in the “microprocessor” world because of an MMU.

I argue because the new PIC has an MMU, single core hardware visualization, and can run a HLOS, it’s no longer a micro-controller at all. After all the core is what we are talking about and it started life in SGI workstations running IRIX.

I agree with everything except the “it started life in SGI workstations running IRIX.” bit. MIPS existed before those at SGI started using them.

Mike “Banned from SGI.bad-attitude” McDonald

The traditional microprocessor usually require some external memory before it would even run where as a microcontroller can run stuff without additional chips. Most of the I/O lines on a microcontroller thus are freed up for for peripherals. Some high end microcontrollers can use external memory, but in doing so ties up a lot of the GPIO lines.

I think it is best to talk about SoC rather than micro-processors because really the processor by itself can’t do much.

External memory must be configured to be used so in fact yes, most SoC can run without external memory.

For instance look at the features table here http://www.ti.com/lsds/ti/processors/sitara/arm_cortex-a15/overview.page?paramCriteria=no you can see the processor has access to at least 2MB of SRAM in package.

The am5k2e02 (2x cortex-a15) has for instance 32 GPIO pins besides the bunch of internal devices, bus controllers and so on. Of course pin multiplexing can be a problem but probably not worse than for micro-controller as these chips are mostly packages in BGA with hundreds if not thousands of pins.

A microcontroller includes a small CPU core, memory, and I/Os. The CPU core in question (MIPS M5150) is comparable in area, speed, process node etc. to Cortex-M3/M4, therefore I categorized it is an MCU-class processor.

The fact that we’ve been able to squeeze in an MMU, high-performance DSP and hardware virtualization is a bonus on top of the standard MCU feature set.

Hi everyone,

I wrote the blog article on Microchip and MIPS M5150. There seems to be a bit of confusion here. M5150 is not microAptiv. microAptiv was indeed used in a previous generation PIC32MZ family. My blog article talks about a new family, called PIC32MZ EF.

PIC32MZ EF uses a MIPS M5150 MCU which is built based on Release 5 of the MIPS32 architecture. Release 5 adds a few new things to the MIPS architecture, including full hardware virtualization. We have three CPUs announced based on this family: P-class P5600 and M-class M5100 and M5150. P5600 is a high-performance core aimed at application processors (think Cortex-A). M-class M5150 competes against Cortex-M3/M4-type CPUs but (and this is the point the article is making) it has a few tricks up its sleeve.

Firstly, DSP performance which is much higher than equivalent MCUs.

Secondly, full hardware virtualization with support for up to seven guest operating systems. No other microcontroller has this functionality present. The point the video and my article are making is that you can use hardware virtualization to run multiple operating systems side by side under a light hypervisor (in this example, SELTECH FEXEROX). Before, you needed either a) multiple chips or b) a high-end CPU (i.e. not Cortex-M) that had virtualization.

Hope this helps, let me know if you have any questions.

Regards,

Alex.

Domnul Voica,

Bună ziua! Abia aşteptatem, spre ştire sa va rugam pe tine.

Can you please convince the folks at Imagination unlock the drivers for the PowerVR GPU stacks to run OpenCL (either with Ubuntu, Linaro or any generic linux or rtos) . That would be awesome.

Thank you for your time.

Sincerely,

Ioan.

Haha, nice Romanian skillz. I am doing my best to promote this activity but we are a big organization and there are multiple groups that need to be involved. The good news is that there are ongoing discussions at least. Secondly, we are working to update the SGX binary drivers to a more recent Linux kernel. For example, the Creator Ci20 dev board (http://www.imgtec.com/creator) has been running Debian 8 based on a Linux kernel 3.18 LTS.

I know it’s not what you’re asking for but at least it’s start. Hopefully things continue to improve.

I can speak it well and read it. Born there, grew up here. Yes, my pronouns during writing need work.

Considering the entire client list I’d understand if say Nintendo, Apple and various others wouldn’t want the code base opened up. Even if it was a binary blob. TI seems too big. Allwinner stuff has a bad rep with the FOSS community.

I’d say see if MediaTek would be willing., And hopefully sell through Digikey or something similar.

MediaTek MT8117,MT8121,MT6589,MT8389,MT8125,MT6589T,MT6589T [SGX544]

and a far flung hope of Cortex-A53 (for 64-bit computing)

MediaTek MT6595M, MT8135, MT6595, MT6595T, MT6795 [G6200]

MediaTek MT8173 [GX6250]

There are several platforms shipping with OpenCL drivers on Android at the moment. Register here (http://imgtec.com/programmes/opencl/) but also check out these blog articles for more info:

– http://blog.imgtec.com/powervr/the-powervr-imaging-framework-for-android

– http://blog.imgtec.com/powervr/heterogeneous-compute-case-study-image-convolution-filtering

– http://blog.imgtec.com/powervr/deep-dive-opencl-face-detection-on-powervr

The best device to buy right now for OpenCL on PowerVR is Asus ZenFone 2.

“The uiTRON system controls a motor, and the Linux boots and restarts, without affecting the real-time system. Try doing that with any of the dozens of ARM Linux boards out there.”

Freescale Vybrid (heterogeneous ARM based microcontroller), the Cortex A5 in there can reboot without touching the neighboring M4 which would typically be running a RTOS. There are several cheap boards featuring these parts out now.

Also Altera Cyclone V SE or Xilinx Zynq, both cases the ARM can be hard reset without touching the configurable part which might be used to host a soft core running a RTOS.

Used em all. They’re all good.

The platforms you mention are SoCs (MPUs, however you want to call them). Here we are talking about microcontroller-class processors that consume less power and fit inside smaller form factors.

Before the MIPS Warrior generation, you needed multiple chips to run multiple operating systems (as you highlight above, a combination of Cortex-A/R and -M CPUs was required for Linux and a real-time OS, respectively). But with virtualization, you have one CPU (i.e. one chip) running multiple OSes in isolated containers. In addition, this MIPS virtualization tech also enables you to run not only two, but up to seven guest OSes on the same platform using only one MIPS M-class based chip.

This is an open-source hypervisor that delivers full-virtualization on PIC32mz SoC: https://github.com/prplfoundation/prpl-hypervisor