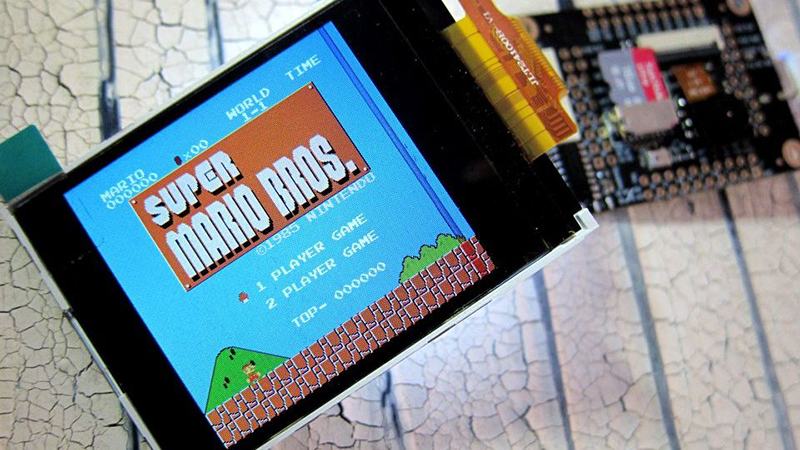

RISC architecture might change the world, but it runs an NES emulator right now. That’s thanks to MaixPy, the new MicroPython for the K210, the recently released RISC-V microcontroller that’s making waves in the community. [Robot Zero One] has the tutorial and [Other Dave] of EEVBlog has a video of the thing in action.

The Sipeed K210 came to the English-speaking world in the form of a weird pre-order thing on Taobao last October promising a dual-core RISC-V CPU for just a few bucks. Seeed, the same people who brought the ESP8266 into mass distribution quickly latched on and started selling modules last February. Now, Seeed is looking at a Raspberry Pi hat using a Sipeed module, and the future for RISC-V microcontrollers is looking great. Now someone just needs to write some software. That’s exactly what the engineers at Sipeed did, and somewhere in one of the released binaries there’s an NES emulator.

The parallel to the question of if something can run Doom is if something can run an NES emulator, so with the release of MicroPython support for the K210, the obvious thing to do is to release an NES emulator. The hardware required is a Maix M1w Dock, available from Seeed and Banggood.

The new support for MicroPython is great, and an NES emulator is amazing, but this should really come as no surprise. From our first hands on with the first Open Source microcontroller two years ago, RISC-V was obviously faster. Now it’s cheap, and we can’t wait to see what’ll come next.

Faster, cheaper, better? Pick any two.

Why?

That’s the thing about technological shifts (including open licensing), you sometimes get to pick all three.

You gonna tell me I need to pick just two in comparing, say Si transistors with tubes? Internal combustion vs steam? etc.

I think you mean, “good, fast, cheap. Pick two.” https://en.wikipedia.org/wiki/Project_management_triangle

I’m quite new to the embedded world. What are the benefits of this board over existing solutions like ESP32 oder a Pi Zero?

RISC V is a new architecture that is completely open source which makes it pretty much unique in the commercial microprocessor world. It doesn’t really have the same use cases as either of those two.

Pi zero is a full computer, esp32 is a wireless board and microcontroller. This is one implementation of a new open-source microcontroller architecture called RISC-V, which is already great because it’s open source, and is expected to make a slew of cheap chips because manufacturers won’t have to pay royalties on the designs. If I recall correctly, WD already plans to use it (if they haven’t already) in new hard drives. SiFive is the main group behind the current chips, but the chip featured here was made by AllWinner. SiFive chips have already been used to make a full desktop running linux (debuted here on hackaday some months ago), but they’re still expensive and not ready to be your next desktop processor. Where they’ll really shine, it seems, is as microcontrollers and incorporated into SoCs.

It’s not going to make ‘cheap chips’. Licencing is a tiny fraction of the SoC cost. However, if you’re in the business of buying millions (ie WD/Samsung-size purchasing of ARM cores) of licences, it’ll save you quite a bit of cash.

For the hobbyist, it’s going to make bugger-all practical difference.

You have half the answer there. The open licensing makes this attractive to very large customers, which in turn means fabs will be spun up to support those customers. And then I expect – because of the openness compared to ARM – to see the fabs iterating designs to meet the markets that they perceive, rather than waiting for a SOC integrator like ST, Broadcom or Freescale to generate new chip designs.

If nothing else, I expect to very soon see an open Zynq-like chip appear with a RISC-V and some sort of FPGA with an open toolchain.

As per usual, us small-scale (qty 1-1000) hackers feed off what is basically supply-chain leakage. If RISC-V becomes popular due to lower license costs, then this will result in cheaper chips eventually.

You think we get cheap micros because there’s a market of “makers”? Hell no. It’s because there are a few products being sold that include tens of millions of PICs, AVRs, ARMs, 8266, and whatever else.

There already is cheap chips. How much lower can one get before companies are paying us to use them?

RISC V is an open source microprocessor instruction-set architecture (ISA). It has spawned a number of open source implementations of the RISC V ISA.

This is a RISC V based micro-controller from Kendryte (not Allwinner). I assume that Kendryte is using its own IP for the cores.

under performance viewpoint, we can say: “nothing”.

but under medium/long term perspective, this can be the knife that will cut the throat of ARM, AMD, Intel.

RISC-V has an enormous potential, it can be siliconed without pay royalties. It means it will be cheaper to produce and can be everywhere, it can scale form 8 bit microcontroller up to N-core at 64 Bit.

We are living the rising of a New Era. Linux is starting to support RISC-V, we can hope in a quite total free (free as a beer) PC that is “open” both in software than in hardware. Now you cannot avoid to be spied by Intel “not-secret-anymore” controller that can bypass all the software security: the ME is “hard coded” inside the CPU and is NOT under the control of end user but can be controlled by Intel… the same for AMD, of course. So, to have OPEN architecture can allow (in theory) to everyone to build up his own CPU out of control of evil companies that in some way has to report yo the Big Brother (USA government). There are many sign that USA power is (finally?) starting his sunset in favor of Far East rising. Honestly, only the time will tell us who is the worse.

The RISC-V architecture specification is open source but this doesn’t mean that any particular implementation is. An implementor or vendor is free to insert whatever management engine or closed source components they want into the final design.

Also the architecture doesn’t scale below 32 bit.

Once again, gamers are advancing the art.

Thought that was porn?

Luckily for this particular project Dave2’s office was spared from the flood.

The open-source gods have shone their light on him for promoting RISC-V

One concern I have with this is fragmentation. If 10 companies are making chips what is the likely hood of them all being cross compatible? Same instructions available? I love the idea of RISC-V and how it does disrupt the processor segment a little but it could kill itself if there are so many varients with slightly different instruction sets.

Or am I barking up the wrong tree? LOL

This is a concern, but the RISC-V people seem to be doing what they can to mitigate it. I believe licensees to RISC-V have to pledge to maintain basic compatibility. Other companies also won’t benefit as much from the RISC-V ecosystem if they make their chips incompatible with the basic instruction set (as used by compilers and operating systems). There are specific places reserved in the instruction set encoding for “vendor extensions” (which are presumed to be incompatible).

The same board now has a playable Quake port… https://robotzero.one/quake-kendryte-k210-risc-v/