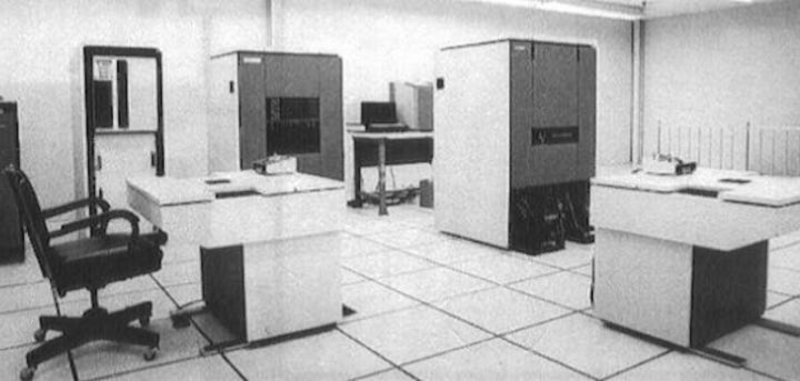

According to [MTSI], if you used a Z80 chip back in the 1980s, it almost certainly passed through the sole Fairchild Sentry 610 system that gave it the seal of approval.

The Sentry was big iron for its day. The CPU was a 24-bit device and ran at a blistering 250 kHz. Along with a tape drive and a specialized test bed, it could test Z80s, F8s, and other Mostek products of the day. There was a disk drive, too. The 26-inch platters stored under 10 kilobytes. Despite the relatively low speed of the CPU, the Sentry could test devices running up to 10 MHz, which was plenty for the CPUs it was testing. The actual test interface ran at 11 MHz and used an exotic divider to generate slower frequencies.

According to the post, an informal count of the number of chips in the device came up with around 60,000. That, as you might expect, took a huge power supply, too.

From some 1975 corporate literature:

“Optimized for engineering, sophisticated production needs, QA and test center operations, the Sentry 610 is the most versatile analytical tester available for engineering and production. It can perform the widest range of tests for the broadest range of components. At user option, the Sentry 610 can perform high-speed MaS/LSI, PCB, and bipolar tests simultaneously. It offers complete testing at the wafer level and through automatic handlers at full-rated device speeds up to 10 MHz. The wide choice of peripherals gives the Sentry 610 system massive data handling capacity to manipulate, analyze, compute and generate reports on test procedures in analyzing MaS/LSI.”

These days, you are as likely to stick test hardware on the IC as have a big machine on the outside. And even then, you probably wouldn’t have something this elaborate. But in its day, this was high-tech for sure.

The Z80 sure has had a long lifespan. It shouldn’t surprise you that Z80s need to be tested, just like everything else.

And the price was ???

If you have to ask, you can’t afford it.

That would be a great way for Waitrose to save money, stop printing price labels and just take all of the customer’s money off them at the till; and if anyone enquires on prices, give them your answer along with the gentle suggestion that there is probably an Aldi or Lidl not so far away if they don’t like it.

I was told a million usd back then. (op)

ESP32-C6 Microcontroller WiFi 6 Development Board with Pre-soldered Header RISC-V 32-bit Single-core Processor 160MHz Support WiFi 6 and BLE 5 Support Raspberry Pi Pico Expansion Boards for AIoT.

$13.49. :)

From the article it links to.

It was introduced in 1971. It lived in a raised floor room. It had 60,000 IC chips, a mix of TTL and ECL. Looking at a July 20, 1970 issue of Electronics magazine,

https://www.worldradiohistory.com/Archive-Electronics/70s/70/Electronics-1970-07-20.pdf

Hm. Page 147/158 of the pdf shows a crisis in Europe. TTL has tumbled to 20 cents a gate in quantity. Now most of the TTL in that machine would be things like quad NAND gates and dual D flip flops. So 4 to 12 gates per chip, say $0.80 to $2.40 per chip. Even if all of the chips were TTL, that would push just the silicon cost to over $100k. But some of it was ECL. Later in the decade, when it was more common, it typically ran closer to $100 a chip, even for simple chips. Even at half that, it wouldn’t take much to push silicon costs alone to be a multiple of that $100k.

TLDR; not cheap.

You have to remember that this was probably bespoke test equipment. And for the semiconductor industry, no less. Probably not less than $1 million, I’d guess, for a nice round number. (Apologies, my estimate may be in mid-80s/early-90s dollars. BTW, There was 400% inflation between 1971 and 2006, the bulk of which was in the 1970s/early-80s)

About one milion dollars in 1974. We had one Fairchild when I started there, and 10 a few years later. My son posted an article on this at mitsi.com on our case studies and just saw it here on my favorite geek placee.

“Call”

Some other very interesting retro stuff at that linked site, like “We Picked Apart the Milestone HP-35 Calculator” https://mtsi.substack.com/p/we-picked-apart-the-milestone-hp

Mmm. Looks like the goodly grain of Tri-X.

The good old days. Slippery potassium solutions and the sharp tang of stop bath!

I don’t miss the smell of fixer on my fingers for hours after a stint in the darkroom though.

This.

To this day I can still recall the exact smell of fixer. It absolutely Would. Not. Wash. Off.

STM32F

ARM Cortex-M3 core at a clock rate up to 72 MHz.

The Flash memory for XL-density devices has density of up to 1 Mbyte, for other devices density of up to 512 Kbytes. …

Embedded SRAM feature up to 96 Kbytes of static SRAM.

SHILLEHTEK Pre-Soldered Authentic STM32F103C8T6 ARM STM32 Minimum System Development Board Module STM32F103C8T6 Core Learning Board.

$8.99

Can it run 64 bit floating point memory register technology programmed in transparent portable gcc c?

Now arriving today 12:45 PM – 2:45 PM

No discarded bits as in Nvidia AI 32 bit hardware floating point high power consumption accelerators. :(- –

Not in 1976 it didn’t!

We will laugh at the specifications of the STM32F in 48 years too!

Yes, as we tend from our campfires cooking our meager meals in pottery.

We’re running up against the fundamental laws of physics as we understand them today. Unless the wild claims of quantum computing come true or there’s some sort of unforeseen breakthrough, we’re not going to see a 1000x clock speedup in the next 50 years, nor 100x. Probably not even 10x.

https://github.com/rejunity/z80-open-silicon

Regarding “These days, you are as likely to stick test hardware on the IC as have a big machine on the outside. And even then, you probably wouldn’t have something this elaborate. But in its day, this was high-tech for sure.”

It is true that many chips have (automatically inserted) test hardware connected internally using a serial JTAG “scan chain,” and indeed this is useful for finding static faults, but this is no substitute for testing chips at speed. For that you need expensive testers, which are almost always at the cutting edge of speed, employ wafer-scale probes, and are very expensive. Time on a chip tester is more costly than a phone call with a lawyer. The longer your chip is connected to the tester, the higher the “price tag” of your chip. So, to come full-circle, it does behoove the chip designers to include hardware fancier and faster than JTAG to help the expensive chip testerquickly test all the functionality of the chip and make sure it meets the speed specs at all four “corners” of the temperature-voltage range.

Pure speculation from someone who left the semiconductor industry just as voltage regulator started routinely appearing on chips: Aha! Maybe it is this four “process corners” testing issue that is one reason why. If you can guarantee that the chip’s internal power rails are always at one, carefully regulated voltage, then you only have to vary the temperature during testing, thus halving the time on the chip tester. Can anyone confirm or deny this?

From a memory test engineer’s viewpoint (1979-2019), one of the basic things you could do is exercise (test) the device at lower and higher voltages than what is stated as the low and high limits in the datasheet. This essentially guarantees that the device will function as designed at nominal voltage. The same thing applies to temperature; apply cold and heat on the device in excess of the datasheet limits while testing. That covers the four process corners: low voltage low temp, low voltage high temp, high voltage low temp and high voltage high temp. Along with voltage and temperature, the other basic thing you could change in testing was timing; running the device at faster than normal speeds (i.e., overclocking) and testing that data setup, hold and access times were checked. In most cases you would only do two corners in production testing in order to save time (and money). The CMOS processes used in most of the memory devices I wrote test programs for was known to operate at two worst corners: slow and fast. Slow was low voltage and high temp. Fast was high voltage cold temp. At wafer sort (testing the devices while still part of the silicon wafer) the slow corner was typical. One would use a wafer sorter (like the Electoglas stated in the article) that had a hot chuck option. That meant you could heat up the entire wafer while testing each device. The test program used at wafer sort would be designed to test the device at lower than normal voltages. Devices that failed the test would be marked (small ink dot applied) so that when it was time to cut the wafer up into individual chips, you would known which ones were good. Once the chips were assembled into their final packages, then you could test them at the fast process corner, where it was more practical to test at cold temperatures (due to the fact that you need to insulate the test environment better to prevent moisture and icing).

At Mostek we would do this sort of corners testing in real time. It only at hot. Cool was never an issue except for AC Delco Automobile parts.

Cut the power to minimum, write a bit to a 1, max the power supply and write zeros on the memory cells around it to surround disturb that 1 bit. Then when the cap had almost discharged at the maximum refresh time, we would read it to see if it had been disturbed and discharged even the slightest below the data sheet values. We had lovely Tektronix gigahertz scopes and 5.5 digit Dana multimeters to calibrate it all. In 1975 when I was 19 and still in school. Best job possible.

Mhz speed custom power supplies were used. We tried to beat the parts every way possible.

Another tech, same shift, same school, same scholarship but from another state built the power supply into a guitar Amp by laying out a singled sided pcb. He got a B in lab because the prof didn’t like that he had left the back of the case off. Same class, I made a wired wrapped Gems 8 bit cpu from a custom Olivetti microprocessor that was never released to the public.

I got a B. Fml

If I recall, these testers cost $1-3M depending on the configuration. Priority was given to production testing and 2nd-3rd shifts we allocated to Test and Product Engineering if experiments or correlation studies were needed. Back in those days (and probably the same today), testers were always developed using the last generation of technology trying to test the newest chips at least 1 generation more advanced than the testers. These testers needed handlers where multiple tube’s of packaged chips “fed” the tester to test units. Most tests were done within 5-7 seconds and these test patterns were put in sequence to catch failures as fast as possible by test/product engineers to increase throughput. Besides the handlers, they might have to heat or cool the device under test “DUT” depending on commercial, industrial or mil/aero specs. If the process and specific chip was well characterized, some tests could be waived.

If a silicon process was not stable, expensive burn in for various time periods would be performed before functional test.