[Mike Field] just finished implementing SPDIF generation on an FPGA. SPDIF is an industry standard for transmitting digital audio signals; the acronym stands for Sony/Philips Digital Interconnect Format. It’s been around for more than a decade and since it’s found on most home-audio equipment, building an SPDIF output into your projects may be quite a desirable feature. [Mike] mentions several ideas for this functionality like building high-end test equipment, or providing a high-quality output for electronic instruments.

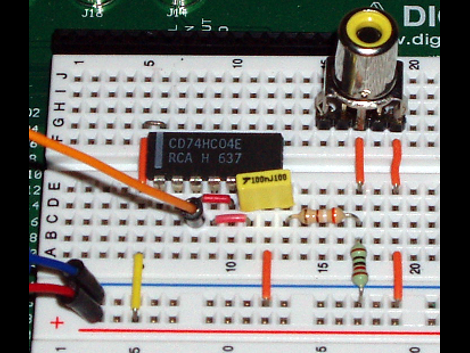

He first jumped into analyzing the specification in order to determine the hardware requirements. Due to some issues with jitter, he found it necessary to use a 100 MHz clock signal. This pushes the jitter down to +/- 5ns of jitter, which he concedes may raise the hackles of audio purists, but does satisfy the published standard. Output requires just one pin of the FPGA and the five components seen above. A hex inverter (74HC04) voltage divider, capacitor, and RCA connector transmit the 0.5V signal to your audio-receiver of choice. Of course, since TOSLINK fiber optic connectors use the same protocol, you could redesign the output and make this an optical connection.