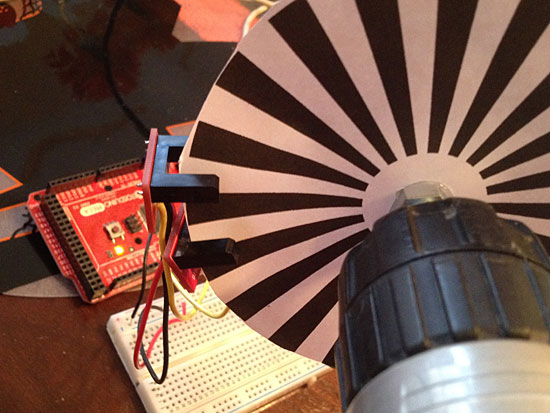

[Pete] needed a rotary encoder for one of his project so he set out to build his own. As the name implies, a rotary encoder measures rotation by encoding “steps” into electrical signals which can be measured by a microcontroller (or used in numerous other ways). Knowing the degrees of movement for each step will allow you to calculate precise distance traveled in applications like robot wheels. Or you can simply use the rotating shaft as an input device which navigates menus or settings.

This concept is a good one to understand. We had originally planned to build rotary encoders for the multi-person Duck Hunt at Hackaday’s 10th Anniversary but the build-off crew had difficulty getting the system to work. In [Pete’s] case he’s using photointerrupters (apparently the IR beam is easily detected through the white paper but usually these parts would be cut out of the disk). We were using reflectance sensors. Either way there’s a trick to detecting which direction a rotary encoder is turning. We’ll explain that for you after the break.

Continue reading “Which Way Are We Going? Concepts Behind Rotary Encoders”

We’re not really interested in building a dummy load like this one for ourselves. But the concepts behind its design make for a nice little mental exercise as you read your way through the build description. [Pabr] wanted to build a dummy load which could be used to test a cheaply made gas generator. He wanted it to be as simple as possible, while providing a range of different loads. What he came up with is

We’re not really interested in building a dummy load like this one for ourselves. But the concepts behind its design make for a nice little mental exercise as you read your way through the build description. [Pabr] wanted to build a dummy load which could be used to test a cheaply made gas generator. He wanted it to be as simple as possible, while providing a range of different loads. What he came up with is