In vehicle racing, a properly tuned suspension is essential for making good time around the track. Weekend Race Warrior [Julian], thought that his right rear suspension might be bottoming out when making hard left turns. After thinking about it for a while, he came up with a super simple way to measure how many times his suspension bottoms out during a lap: a digital counter made from a calculator.

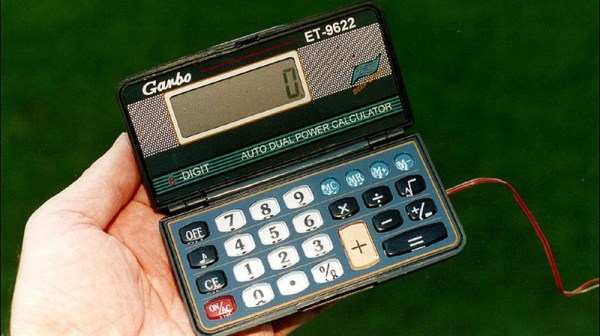

There are two types of calculators out there, one is good for this project and the other won’t work. To figure out which one you have, type in 1+1=. All calculators should display 2. Then, press the = button again. Some calculators will continue to show 2, but some will change to 3, then 4 and so on as many times as the = button is pressed. This is the type of calculator this project requires.

[Julian] opened up his calculator and soldered a pair of wires across the = button terminals. After a hole was drilled in the case for the wires to exit, the calculator was put back together. To count how often his suspension bottomed out, a normally open limit switch was installed on the car at a point where it would be triggered when the suspension bottomed out. The 2 added wires coming out of the modified calculator connect to that switch. Switch presses now emulate a = button press. Before starting a lap, 1+1= is pressed to display 2. At the end of the lap, if the suspension bottomed out, the switch would be triggered and the displayed value would increase. Remember to subtract 2 from that value to get the total number of events that occurred.

A mechanical switch makes this a great application for counting when things move a certain way but there are some more options. Connecting the switch-side of a relay to the calculator allows [Julian] to count brake presses (via the break light signals) or count how often his boost pressure goes over a certain amount (using a pressure switch).