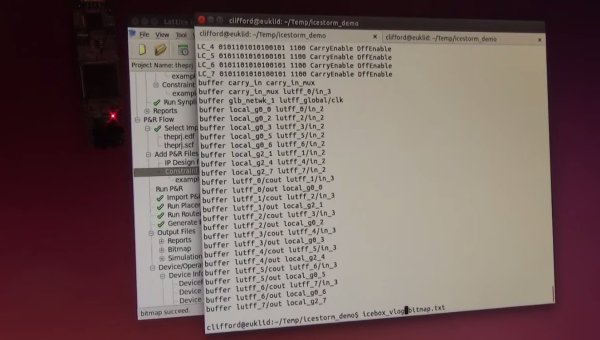

FPGA development has advanced dramatically in the last year, and this is entirely due to an open-source toolchain for Lattice’s iCE40 FPGA. Last spring, the bitstream for this FPGA was reverse engineered and a toolchain made available for anything that can run Linux, including a Raspberry Pi. [Dave] from Xess thought it was high time for a Raspberry Pi FPGA board. With the help of this open-source toolchain, he can program this FPGA board right on the Raspberry Pi.

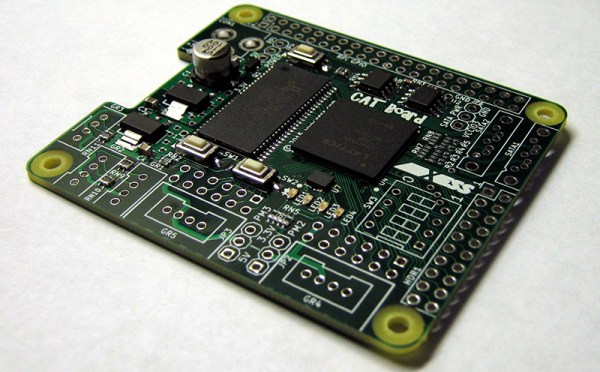

The inspiration for [Dave]’s board came from the XuLA and StickIt! boards that give the Raspberry Pi an FPGA hat. These boards had a problem; the Xilinx bitstreams had to be compiled on a ‘real’ PC and brought over to the Raspberry Pi world. The new project – the CAT Board – brings an entire FPGA dev kit over to the Raspberry Pi.

The hardware for the CAT Board is a Lattice iCE-HX8K, 32 MBytes of SDRAM, a serial configuration flash, LEDs, buttons, DIP switches, grove connectors, and SATA connectors (although [Dave] is just using these for differential signals; he doesn’t know if he can get SATA hard drives to work with this board).

Despite some problems with his board house, [Dave] eventually got his FPGA working, or at least the bitstream configuration part, and he can blink a pair of LEDs with a Raspberry Pi and programmable logic. The Hello World for this project is done, and now the only limit is how many gates are on this FPGA.