These days we’re used to our devices containing an inertial measurement unit (IMU) that lets it know its position relative to the Earth. They’re mechanical devices at heart, and so they’re not infallible, with a few well-known failure modes — but we can try and help it. One way that’s getting some attention is to put many MEMS IMUs on a single PCB, connect it to an FPGA, then process their data all together to make for a more sensitive IMU or filter out drift. Want to join in? Here’s an open source implementation from [will127534].

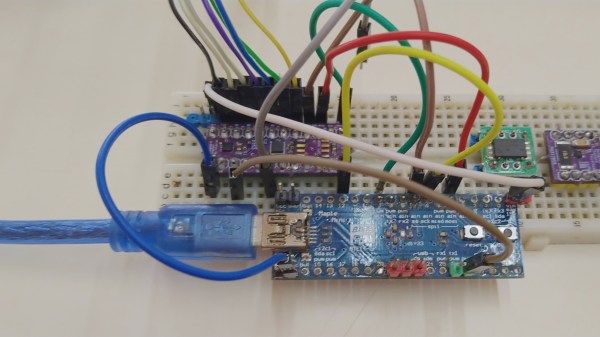

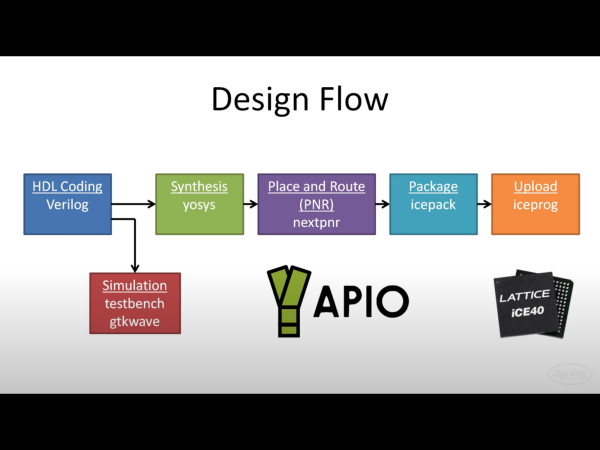

With 32 individual ICM-42688-P SPI-connected IMUs and the beloved ICE40 chip at the center of the board, this PCB is a powerful platform to help you jump onto the new direction of the IMU research world. There’s example Verilog code that tests the board’s workings, and you can pair it with a Pi Pico running MicroPython to test out its raw capabilities. After that, the stage is yours.

The board is cheap to order online, easy to assemble yourself if you must, or have JLCPCB assemble it — just solder some capacitors on the backside afterwards. There’s a breakout, but it’s mostly for tests. This board is very much designed to be a module in a bigger system, [will] mentions that he’s building a geophone. Clever array-based hacks are en vogue, it would feel – here’s a LED array from [mitxela] that uses LEDs as sensors.