RISC architecture is gonna change everything, and I still can’t tell if we like that movie ironically or not. Nevertheless, RISC-V chips are coming onto the market, chipmakers seem really interested in not paying licensing fees, and new hard drives are shipping with RISC-V cores. The latest development in Open instruction sets chips comes from OpenISA. They’ve developed the VEGAboard, a dev board with two RISC-V chips and Arduino-style pin headers.

The VEGAboard comes loaded with an NXP chip which combines an ARM Cortex-M0 and Cortex-M4. So far, so good, but there are already dozens of boards that combine two ARM microcontrollers on a single development platform. The real trick is the RI5CY and Zero-RI5CY chips on the VEGAboard, a 4-stage RISC-V RV32IMCCXpulp CPU. This comes from the PULP platform, meant to be a small, low-power, but parallel platform for various processing needs. In short, with the VEGAboard, you’re not running a blink() sketch on the RISC-V microcontroller. You run the blink() sketch on the ARM microcontrollers, while using the RISC-V chip to read accelerometers and toggle pins. It’s a coprocessor, but it’s RISC-V.

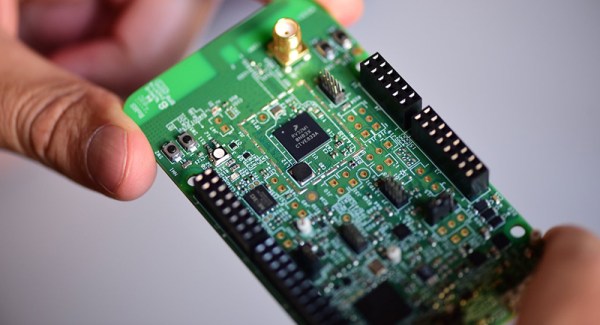

Other features of the VEGAboard include 4MB of Flash, a light sensor, accelerometer, magnetometer, an RGB LED, OpenSDA serial debug adapter, an on-board BLE radio, and of course those wonky Arduino pin headers.

There are, or were, free VEGAboards available, but those are long gone. It’s still an interesting platform, though, and if you’d like to get your hands on one, production will resume shortly. Of course, if you need RISC-V right now, there are actual RISC-V Arduinos, a RISC-V with built-in neural networks, and SiFive will soon have a Linux-capable RISC-V multicore board. These are exciting times, and every day we’re seeing how RISC architecture is gonna change everything.