For last year’s Hackaday Prize, [PK] tried to build a video card for microcontrollers and headless Linux systems. It was only 640×480 resolution VGA, but the entire project was designed around a CPLD communicating with a microcontroller over SPI. This prize entry was, by [PK]’s own admission, a failure. It was late, but now he’s had an entire year to perfect his design. That means he can enter version two of his VGATonic in The Hackaday Prize.

The VGATonic version 2 uses a Xilinx XC95144XL CPLD for the VGA timing, and an ATTiny 2313a to read the SPI bus. Video memory is four megabits of static RAM. That’ls pretty much all you need for the most basic VGA graphics card, and all of this is packed onto a 3×3 inch PCB.

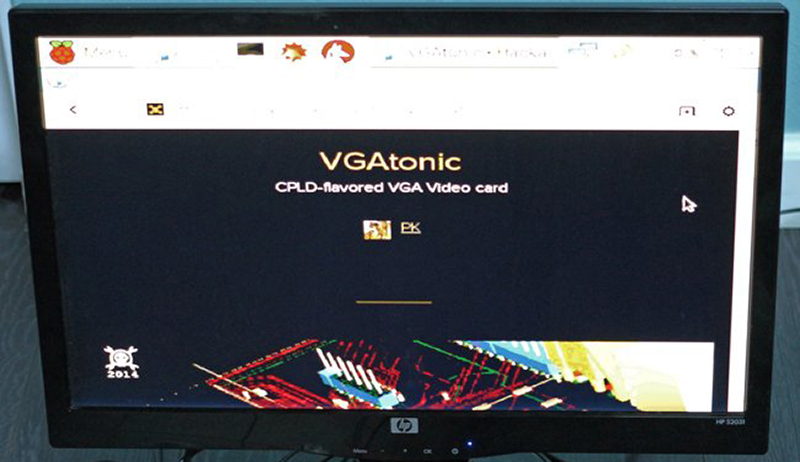

You can do a lot with 640×480 8-bit graphics running at 25FPS. In the video below, [PK] has a ‘hello world’ of sorts, Doom, running on a Raspberry Pi 2 with his SPI graphics card. Yes, it’s a graphics card for the Raspberry Pi, and it looks really good.

Further refinements of the design will include some primitive graphics routines. Not OpenGL or anything fancy, just something to reduce the number of writes on the SPI bus. It’s a great project, and perfect if you want to add video out to an Intel Galileo or other microcontroller project. [PK] has a video demo, you can check that out below.

Very cool! Nice, stable signal too. How are you guys handling SRAM refresh? FIFO?

Ahhhh. Did it again! Move that damn Report Comment Button to the left HAD!!!

Now for the comment: Why would you need to refresh static ram?

Sorry, temporary brain fart as a result of trying to do that same thing with the Papilio Pro’s SDRAM. That does, however, my question.

This is why HAD needs a delete button as well :)

And an edit button. And coctails with tiny umbrellas :-D

and cocktails with GIANT umbrellas!

An actually usefull, great, great application! Bravo!

FWIW, there is a graphics card for the Intel Gallieo already, it fits in the mini-pcie slot

http://www.micropassion.co.uk/Graphicscards.html

maybe this will finally help linux get to year of the desktop.

Common man. Stop picking on linux

I don’t see that happening anytime soon, but that would be pretty awesome, I would love to see that happen. But doubt it ever will.

It’s hardly matters. Linux already has cellphones and servers dominated. People kinda medium like chrome books.

So it would seem that from the examples it dominates in areas where you have a tech support team or OEM that take cares of the configuration/management/customers support.

Great to see this project.

Is there space left in the CPLD to implement a seamless switchover between serial terminal, and gfx card mode or even an overlay of the terminal chars over the gfx?

With the demo you’re seeing, the ATTiny is underused – all it’s doing is bitbanging SPI to the programmable oscillator to get us 2xthe VGA pixel clock. All of the SPI code is directly on the CPLD.

I put serial mode (and of course, terminal emulation) as a stretch goal for this year because I am running short on macrocells, but I might be able to employ some tricks on the uC side to get some of them working.

With 4Mbits of SRAM you could in theory increase the resolution to 800x600x8bits. Other than that I’m surprised that you can push data fast enough over SPI to manage 25 frames/second, I make that to be about 60Mbits/sec.

I “Believe” because it’s not pushing video, it’s pushing sprites and manipulating them. It’s pushing instructions, that are then rendered by the card.

Sorta the difference between trying to reproduce a Monet, and sending a black-and-white line drawing of a Monet with “paint-by-numbers”

4Mbits would then be for the sprites and frame buffer

P.S. is the Vsync issue the CCD on the camera or an issue with the video card

No, there isn’t any room for sprites or much of any instructions with my implementation – I’ve only got 144 macrocells to mess with on the CPLD. It’s just saturating SPI, and every time I reset the chip select there is some logic on the CPLD to reset the memory writes to 0,0.

So it’s painting the Monet a pixel at a time, in this case.

The link to his project page says he is driving SPI from the PI at 62.5 MHz.

Pretty impressive !

Could it be used to bring vga to mircocontrollers/soc that have no video output ?

Or is 62Mhz an unusually high frequency for SPI ?

I was thinking to the atheros ar9331 (runs at 400Mhz)

(in this case the spi is bit-banged according to https://github.com/8devices/carambola2/issues/20 )

The SPI really sucks on the 9331 carambola, we used it at the company I used to work for and never could get a lot of stuff running on it’s fake spi.

I was not expecting something great ;)

Thanks for answering

dont bother, get usb to vga adapter instead

there was even a project running nes/snes emulators on a router (or was it a Marvel based NAS?)

hmmm searching searching, there we go:

https://www.youtube.com/watch?v=hwVwFHDA5iE

http://www.hunterdavis.com/2010/11/28/a-25-gamingemulation-powerhouse-using-the-dockstar-as-a-gaming-console/