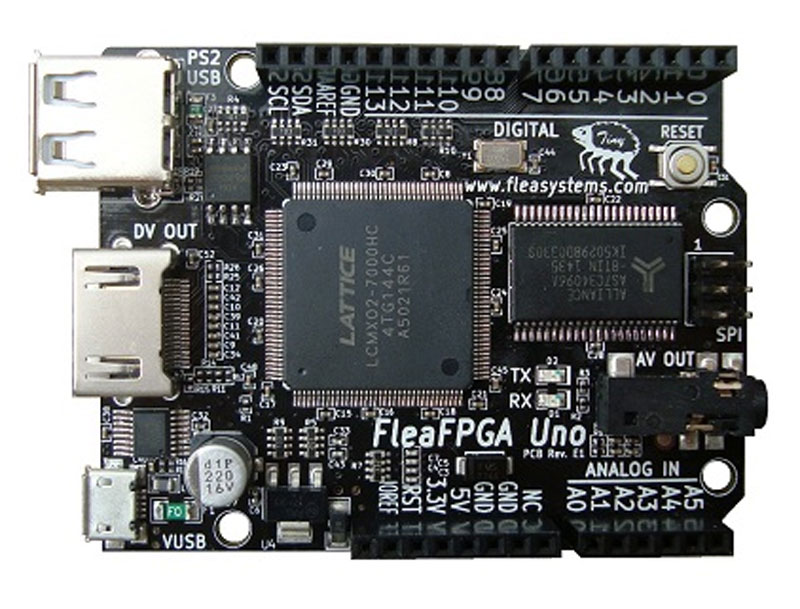

Some things are better together: me and my wife, peanut butter and jelly, and FPGAs and Arduino Unos. Veteran hacker [Valentin Angelovski] seems to agree: the FleaFPGA Uno is his latest creation that combines an FPGA (a Lattice MachX02 700HC) with an Arduino-compatible CPU.

It’s a step-up model from the origional FleaFPGA. With a few other components thrown in (such as a HDMI and composite video output and a WiFi option), you have a killer combination for experimenting with FPGAs or building an embedded system. That is because the Arduino part frees the FleaFPGA Uno from the breadboard: you can easily program, control and interface with the FPGA over a serial line or a wireless link using the Arduino IDE. There is even support for Arduino shields (albeit only 3.3V ones), making it even more expandable. This would be an awesome starting point for a retro gaming system, as many 8-bit consoles can be easily emulated in an FPGA. [Valentin] is currently selling the boards directly, and they are very reasonably priced at $50 or $60 for the WiFi version.

How similar is the MachX02 FPGAs to the iCE40 series?

After hearing about project IceStorm, I’m starting to dabble in FPGAs. Prior to this, I just didn’t see the point — I had bad experiences using proprietary toolchains (TI Code Composer, Rabbit Semiconductor’s Dynamic C, the need for a proprietary gdbproxy for MSP430…etc) and didn’t want to endure that headache again. Not in my own designs.

It’s good that there are more FPGA boards targetted at enthusiasts coming out. A trend I hope to support as the open-source tools improve and gain support for more chips.

AFAIK, There’s no open source support for the MachXO2 parts like there is for the iCE40. Lattice’s Diamond ide/tool set is just as bad as the rest of them, but at least runs on Linux and has a free license for the XO2 parts.

That’s a good question (much better than RÖB comments).

The opensource toolchain for Lattice ice40 FPGAs:

http://www.clifford.at/icestorm/

http://hackaday.com/2015/05/29/an-open-source-toolchain-for-ice40-fpgas/

Another similar project of arduino-style board with a FPGA:

https://hackaday.io/project/6636-iced-an-arduino-style-board-with-ice-fpga

Will there be an opensource toolchain for the MachX02? Are you in contact with the icestorm team?

I don’t know if they are working on an opensource toolchain (I’ve not heard anything about it). The MachXO2 and iCE40 parts aren’t really related (Lattice purchased SiliconBlue makers of iCE40) and I believe MachXO2 is a more powerful and complicated part than the iCE ones (so not “easy”).

Lattice of course does have a freely downloadable IDE Lattice Diamond (registration required). This is similar to Xilinx or Altera offerings but is the smallest of the three to download (“only” ~1.6GB). Also in my experience Diamond is significantly faster at synthesizing a design which is a nice plus (about twice as fast for one design I am working with).

Which comments are you referring to?

Well I am guessing from the part number that the FPGA is about 7000 LEs.

But lattice ??? I wouldn’t have a clue where to start as far as writing VHDL for Lattice goes. JTAG port???

They definitely got the use of SRAM right. Beginners shouldn’t be shoved into building SD-RAM controllers.

But worst of all they chose an Aduino Uno form factor, what a disaster as far as 3.3 Volt “vs” 5 Volt goes. I have never seen a 3.3 Volt shield in Uno form factor and the Uno was about the only variant that didn’t have a 3.3 Volt version AFAIK.

And the price puts up around a competitive area so it will need good documentation and tutorials to compete. I saw little of that at the linked site.

Does the Arduino UNO not use the same footprint as others?

There is the Uno, Mega, Mini, Mini pro, Nano etc. The Mini Pro, Mini and Nano come in both 3.3 Volt versions and 5.0 Volt versions.

I thought they all used the same footprint and pinout. Thus they can all use the same shields save for the voltage and differences is supporting hardware (eg such as analog support).

It’s a bitch finding docs in one location which is probably why I never looked much further into it. Do they all have that annoying pin spacing the original had?

The wider ones like the Uno, Mega and Zero have a very similar pinout and are probably almost identical from a programming point of view.

The others that I mentioned are various forms of Dual Inline Pin boards.

Huh? 3.3V pin is right next to the 5v pin. It’s even there on my old 1st gen RS232 port arduinos.

Thanks for your comments :-)

FleaFPGA Uno’s JTAG interfaced can be accessed via the usb port labelled ‘VUSB’. All that is needed is a valid bitfile, USB cable and JTAG utility for the host PC as outlined in my FleaFPGA Uno User Manual. My user manual can be found on the related project link in the article.

Writing VHDL for a Lattice FPGA isn’t very different from writing VHDL for other FPGA vendors. Challenge for me is to try and get absolute newcomers (ie those with ONLY arduino-level of electronics experience) to be able to use my board.

As for your comment regarding shield compatibility – any shield that has been properly designed to Rev.3 spec should work with my board, among other cases where 5V tolerance is a non-issue.

l’ll take your comments regarding my project site as constructive criticism.

– Yes, my project site for FleaFPGA Uno is still new and ‘work in progress’ and fleasystems.com is still little more than a hobby site :-)

– Yes, it is following the basic theme I had previously used for my earlier FleaFPGA classic board, which seemed to be adequate for nearly two years now.. I welcome any suggestions/comments to help improve things. Thanks!

Dang – if only I had played Tetris Trio more, I could have designed this FPGA device as well! ;-)

Love the link!!!!

Origional?

Basically, FleaFPGA Uno was intended as a simplified version of my earlier effort:

http://www.fleasystems.com/fleaFPGA.html Cheers.

From their website –

What I expect to see –

View Top level VHDL <A href=”top.txt” target=”_blank”>here</A>

Simple!

step 1) Click the link

step 2) Read the HDL

And what they have

click to download zip

step 1) Left Click link

step 2) Choose save as

step 3) Navigate to a location to save the zip

step 4) Create new folder

step 5) Give the folder a name

step 6) Click save file

step 7) Wait for download to complete

step 8) Open explorer

step 9) Navigate to where you thought you saved it

step 10) Navigate to another possible location

step 11) Close explorer

step 12) Open search

step 13) Go back to browser to get file name

step 14) Enter file name into search

step 15) Wait 20 minutes for searh

step 16) Give up on search

step 17) Go back to browser

step 18) Download file again

…

and that’s without even going into the issues with ZIP files.

One of the precepts of web design is that you have to make it as easy as possible for the user. This takes *FAIL* to a whole monumental mind blowing new level – HDL is a TEXT FILE and browsers can actually render TEXT!

How is it that you managed to traverse any portion of the internet without encountering a zip (or any compressed format) file and skirt around the need to download said file, find it on your computer, and open it?

Most bad websites make it difficult to find said file on the site itself. Not lose said file on your own hard drive.

Downloading a zip file to extract and view something that a browser can render is akin to putting all the page images in zip files with links to download and view them. Tell me how many page images would you view if you had to download and extract the .png/.jpg/.gi first?

I understood your point but your example is full-on retarded. How many projects would you download if you had to manually download each and every file individually through your browser?

Managing your compressed files is such a fundamental thing across the internet that losing your files after download just tags you as a straight up amateur at best.

I see no problem with him compressing his files into a zip. It’s so small and web browsers can be configured to deal with them that it barely registers as a blip in my daily work.

Clearly repositories like Github has spoiled you.

I second this. Haters gonna hate :-)

http://www.filedropper.com/myresponse

What – cat got your tongues????

Or is it that you are badgering me while you yourselves are unwilling to download a file to see something that can be rendered by your browser.

We call people like that Hypocrites.

And to [SavannahLion] I reject your “straw man” augment. From the very start my argument was about SINGLE files that can be rendered by a browser not a collection of file most of which can’t be rendered by a browser.

Quote:

“What I expect to see –

View Top level VHDL here

Simple!

step 1) Click the link

step 2) Read the HDL”

or is that not clear to you?

Downloading a tarball or a zip file for a source bundle is a very established procedure. It is this projects fault that you can’t remember where you saved the file? The time taken to search your badly organised machine is also included? Time taken to redownload file because you couldn’t remember anything about the original filename? Did you want to blame them for anything else? If you had to email the author to request the files then sure, that’d be annoying but really? complaining about a zip file?

For people with working browsers and file associations, the steps are:

step 1) Click to download zip file

step 2) Navigate to or create folder to save zip file

step 3) Unzip file

@[NowhereMan]

I covered these point in the link above which goes to a ZIP that holds a TEXT file and my response is in that.

Didn’t you read it?

Or are you another hypocrite?

Or didn’t you realise your buying into a “straw man” argument because this point here is not the point I raised?

Or is it that (shamefully) like me, you simply couldn’t be bothered to download a ZIP file and then extract another file when that file could have just as easily been rendered in the browser in the first place?

Actually, ROB, my ‘top-level’ zip contains TWO files – NOT JUST ONE! FIRST file is a top-level VHDL wrapper while the SECOND FILE one is a pin constraints file. BOTH files are needed if you wish to create new VHDL projects using my board from scratch…

Enough with your negativity and hate already. Just stop.

@[Valentin Angelovski]

Isn’t ironic that the same person who buys into an argument without even realising what the point is with “I second this. Haters gonna hate :-)” and then turns around and says – “Enough with your negativity and hate already. Just stop.”?

There hasn’t been any “hate” in my comments. I am, like most people, allowed to have an opinion and to be honest with you I am generally the one with the more calming approach.

I do appreciate that ‘hackers’ like yourself take the time to ‘create’ the things that you do. I do a little hacking / creating myself and that is perhaps why we have bumped shoulders.

But like it or not the point I made is valid. I wanted to assess your product and my interest expired due to the complexity of doing so. I feel quite safe in assuming many others will do the same as I have also spent many years in wed development and I have spent enough time in log files to know what sustains and kills a browser session.

Just to keep the record straight, you’re not my client and I’m not offering you any advice. Make of it what you choose. I am indifferent.

Just reading back and noticed this – “Managing your compressed files is such a fundamental thing across the internet that losing your files after download just tags you as a straight up amateur at best”

Wow you’ve got it worked out then. I can see you folder structure now –

[]

[-] zip

[-] gif

[-] png

[-] doc

Anyway [SavannahLion] have a look around the hackaday.io site. I’m Hacker 404

The send me a ling to your projects. Or is it that the person that is calling me an “amateur at best” is just a looser full of sh!t.

Oh and the one very very very simple point that you seem to have failed to understand is the people type VHDL in using a keyboard – ie it’s a god damned text file.

Honestly, I don’t understand why you’re so mad about this.

You could simply request politely that the creator put a link to just the VHDL text on the page so it’s viewable, instead of frothing at the mouth and calling everyone hypocrites.

He just said the text file is not the only thing in the zip, it also has the pin constraints and the VHDL itself. The creator just explained why he did what he did.

I also don’t see what the big problem is with zipping it. I’ve seen loads and loads of projects online that where they’re kept in single-file zips, and I’ve never had a problem with any of them.

I don’t see how people here are unwilling to download single files as zips because you’re the only one who seems to have a problem with that, so your hypocrite accusations are absolutely baseless.

I’ve also never lost a single file, because I categorize them into things like “Apps”, “Electronics_Projects”, “Audio_Tools”, and things like that.

Are you old enough that something like this is unfamiliar to you?

Feel free to call me a hypocrite, because then that would mean, A: You didn’t read a word I wrote, or B: You don’t understand what hypocrite actually means.

@ RÖB

Cool down man. And — as far as cats go: I’d download Valentin’s file if it’d interest me. I won’t download your *cleverly* hidden answer because — judging by your other contributions in this thread I *positively know* that I couldn’t care less.

So there you go.

Yeah well download the page. Strip it except for the screen names and also adjectives.

It’s pretty well self explanatory from there. And thanks for the patronisation. I have a good memory and you have endless screen names. Well, unless I notice some things about your writing style.

No one read your filedropper response, RÖB, because this is a comment section. A web site is just that, a site. It’s what the designer wants it to be. You have your idea that all the VHDL should be viewable from your browser, I prefer that non-web files are not even known by my browser for security purposes. Seems this project leans more my direction than yours, tough luck for you.

Now, if said website had required you to go to a secondary site, click through some agreements, wait 60 seconds to even view the VHDL while pron ads played to the side and scripts tried to put super-cookies in every available space, you might have a valid complaint and comparison. As it is, you are comparing apples to oranges, as always, and expecting people to be civil to you and engage in your ego-stroking.

Frankly, the only reason I bothered to reply to you is that I hope that, some how, the dregs of the internet that you represent will realize that the majority of adults out in the real world see your loud-mouthed excess for what it is: childish text-wank resultant of either a disruptive attempt to amuse yourself or, worse, the misguided opinion that you are so vastly superior to the rest of the world that we should all acknowledge you and bow.

As I am not a childish moron, I will abide the societal norm of having a conversation in a conversational setting. If you wish to reply to me (though I humbly beg you not to) I expect you to do so openly in this comment section and without obfuscation.

Github always has a ‘download zip’ button, to download all files in a package )

The zip option is only available at the root level. I was surprise that github actually formatted my BOM into a table and do sensible stuff for common formats. :)

On some brain dead iOS devices, you can’t view the contents of a zip files inside a browser nor have the option of downloading to a directory. Not that I would want to do anything serious on it than watching cat video. So an additional link to github along with the .zip file should make life a bit easier for everybody.

@ROB

You’re acting like a moron. You expect an answer ten minutes after your lame ass attempt to prove a weakling point? Unlike you, I don’t sit around on HaD waiting for responses to my posts. This isn’t a live chat. People actually have, what’s that phrase? Oh right… a life.

I like how you present a “portfolio” of code and claim anyone else who doesn’t is a “loser full of sh!t”. Not even man enough to spell it out properly? Guess what not all of us chooses to share our code in the public. Yep, you guessed it, I’m one of those bastards that writes closed source code. I get paid pretty decent money for it.

I may or may not feel like answering your next crap response, I didn’t bother wasting my time reading all of your existing ones. Surprisingly, I have more important things to do than concern myself with your inability to manage your files.

You SavannahLion are a complete idiot if you think you can jump in here and lambaste people without taking the time to get the very most basic facts right.

People don’t download ZIP files when they’re assessing weather of not they’re interested in a product. Sufficient information needs to be on the web page so that people can make that assessment and perhaps commit to product and start downloading files at that later stage.

[SavannahLion] this means that every bit of sh!t that has dribbled from your keyboard is completely irrelevant.

Then when you don’t seem to be making any progress with your straw man argument you start with the foul language like a spoilt little brat. How was your childhood?

Then when I mention that you’re not a contributor here you claim that you are a well paid close source software developer. That is laughable when you very own profile states “Amateur hacker and broke programmer”. What! are these “Amateur Hacker” projects close source to or is it simply that you are full of sh!t.

All your profile demonstrates is that you can write a profile lol. Go join facebook where you won’t feel so intellectually challenged.

Around here RELEVANT facts are a good way to put your point forward. If you can’t even present relevant information then you best go somewhere else.

@[Harold]

The creator sent this reply to one of my posts –

——————————–

“Valentin Angelovski says:

November 21, 2015 at 6:59 pm

I second this. Haters gonna hate :-)”

——————————–

So he has been offside to me from the start.

His comments were a stupid move really. He has lost most of the benefit of the Hackaday post as the thread here is pretty well trashed by the attitude he supported at the onset. No one is going to wade through all this crap to find out more about his product or what others think about it.

Good gravy ROB/hacker404. Your amazing ignorance is readily transparent when you attach such importance to a profile I set up back when hackaday.io launched and done little to update.

Just how old are you? I don’t give a flying flip about my hackaday.io profile. I don’t attach a lot of importance to what people think of me online so I don’t spend time fretting over social media sites when I prefer to spend my time producing real world things. Not surprisingly, my work does not allow me to post code publicly. I don’t argue with the job and quite frankly, I don’t care if that code never gets published, it’s boring as hell anyways and not for people of your caliber, as it were.

You, however, spend your time measuring posts in minutes pawing away at your keyboard pretending you have something intelligent to type throwing a fit whenever someone points out your ineptitude at even the most basic computer skills.

You can’t even write without cussing properly. Grow up.

@ROB

To clarify my “Haters gonna hate :-)” comment:

It seems to me that you not only almost completely disapprove of my project (apart from maybe your SRAM comment ;-), but you also missed my attempt at humor. My above comment was purely tongue-in-cheek (note the ASCII smiley) to say that I disagreed with notion of not using zip files, which happens to be an interim solution in this instance (please read below). So I see this as a major source of misunderstanding between us already.

You then go on and write:

“So he has been offside to me from the start.”

NOT true! I only began to take issue AFTER you posted repeated negative comments AND in all probability you overlooked (or ignored, I may never know..) my FIRST ever reply (which was to YOU, by the way) in the comments section, that was completely professional and also covered nearly every aspect of your initial and ongoing concerns rather elegantly:

http://hackaday.com/2015/11/21/fleafpga-arduino-uno-fleafpgauno/#comment-2804220

Then there’s this:

“His comments were a stupid move really. He has lost most of the benefit of the Hackaday post as the thread here is pretty well trashed by the attitude he supported at the onset. No one is going to wade through all this crap to find out more about his product or what others think about it.”

I supported nothing beyond an opinion that was different to yours. Others saw *your* comment and likely arrived at the same conclusion. Sorry, but I cannot be blamed for the thoughts or behavior of others. With all due respect, to think otherwise is like saying everyone who disagreed with you was incapable of independent thought :-P

While I am sorry that you did not find my current project status up to your own personal high standard (my site was still a work in progress as I pointed out to you very early on) your extent of negative comments kinda make your last comment seem more like a personal hope than an observation..

Anyways Rob, I wish you all the best with your own endeavors. Cheers Valentin.

Well done [Quin]

What an exemplary effort.

Now lest get down to some nitty gritty.

Firstly, as you confirmed – no-one is going to look at the file dropper response. This was more or less a statement that has been confirmed by all the readers here, that if you make it difficult for people to obtain information then they simply won’t.

Thank you for confirming that Quin, I do have the stats from the file dropper site and guess what – no one (including you) downloaded the file. Is that surprising?

Now Quin we step on to VHDL, well actually we don’t but that’s what you choose to believe like I said above “I wanted to assess your product and my interest expired due to the complexity of doing so.”

This is not specificity about VHDL – rather it’s about getting some handle on the capabilities of the FPGA chip and seeing some VHDL will give me some idea about that because I can actually read VHDL. You didn’t mention weather or not you can read VHDL [Quin] can any one guess why??

And then you say “and expecting people to be civil to you and engage in your ego-stroking”. Well first, I am civil to others and so I expect others to be civil to me and then ego, well I’m not here for that. This site has very very many people that are so experienced and professional in their field that I could never hold a candle to their abilities. I have always been her as “humbly” myself.

Then quote: “Frankly, the only reason I bothered to reply to you is that I hope that, some how, the dregs of the internet that you represent will realize that the majority of adults out in the real world see your loud-mouthed excess for what it is”

And I see where you quoted me … wait you didn’t quote anything whatsoever that I had said! oh ok you made that up.

And then the best – Quote: “As I am not a childish moron”

and that immediately suggests that I am.

Right there Quin – There’s your problem – you got that statement wrong.

Well, you are a childish moron…

Read what you wrote and think again.

Oh, and you projects are … where exactly?

No, the point is nobody is going to bother downloading a ZIP file when it’s just text of some guy moaning in an Internet argument.

Setup files for managing some hardware you’ve bought, you will download. Because that’s worth your time, it has value. Some guy crying, doesn’t.

You see the difference? It’s not the ZIP file people don’t want, it’s your “argument”. The contents of the file. If ZIP files are STILL inconvenient to you… I’ve managed fine since I was a teen and you had to use PKUNZIP on the command line. It’s just not difficult.

Your point is, the text-based file in question is not viewable in your browser because it’s zipped. The text in question is not meant to be read by a casual web browser. It’s meant to be read in the IDE. It’s intended for people who are using the board, and therefore need all the other files too. Keeping the text in with those files, means you know where to find it when actually using the board.

Thus Valentin made the fairly sensible decision anyone else who’s technically literate would.

The fact you can’t even FIND where your ZIP files go… You’re doing Valentin a favour staying away, imagine the shit you’d give him when you lost the USB lead.

Let me get this right.

You go online and google cars and then buy a car and on the page where you bought the cars was an add for a house so you bought that too and then buying that you see an ad for meds (female hygiene) so you but them as well.

Does this sound absolutely ridiculous … yes?

Well that’s the argument you’re presenting to me because I was not in the “purchased product” phase where people would be inclined to download a zip. I was in the “assessing product” phase where people are not inclined to download ZIPs for information to help them assess weather or not to purchase.

Now can you see that you have (in my opinion) bought into some other persons “straw man” argument and at lease to me you now look like a complete fool.

What, of your argument relates in any way to the context of the original problem? Nothing?

Now, I understand that I could have made that clearer and in a normal course of debate/resolution I would have but when I get some idiot that throws in a straw man argument and at the same time lambaste me with foul language then I seriously couldn’t be bothered.

And this is what you jumped into. Do you now realise that everything that you have taken the time to say is absolutely worthless because it doesn’t relate at all to the original problem. Instead your comments relate to a straw man argument created by someone else, and that you were foolish enough to follow.

Oohhhh…kay…..

See, the ZIP file in question is INTENDED for people who are using the board. Using a zip is absolutely the standard way of doing this.

Sure, somebody might want to check out the file first, before they buy. The zip’s freely available to them too. They can simply get the file, unzip it, and check out the files at their leisure.

Because this sort of thing is aimed at people who have at least a small amount of technical ability. How you can comprehend VHDL but not a simple PC file system, is astounding to think about. For every other person in the world who would get any use out of this board, being presented with a zip file is no obstacle.

On the other issue, while I’d be happy to respond to your stupid responses to me all over this site, I’m free enough from psychosis and mania to realise that that would probably bore and annoy all the other readers. So I’ll limit myself to this one.

@[Hassi]

I’m not going to bother to respond in any detail to your comment except to say that tomorrow I will be here with the same name and I will have nothing to be embarrassed about.

Will you still be here by the same name [Hassi]?

Dude, your’re complaining about not being able to use simple file and directory stuff, which has nothing to do with the web page.

If you can’t work a web browser, you’re not gonna do well with FPGAs. You need to find something a bit less technical to do.

Those two skills aren’t mutually exclusive, if his comments regarding how he got started are any indication.

Most of this complaint is about your operating system.

I think his “operating system” is unstable. Not his computer’s, his.

Idiot – oh wait after calling me an idiot you asked me to stop calling you an idiot or how long this is going to go on for or some shit like that.

So you tell me idiot – how long *is* this going to go in for?

I want to try playing with FPGA, can anyone recommend an inexpensive starter board/module I should get as a beginner?

Not really FPGA, but close enough to play with and good price, too ($10).

CY8CKIT-059 PSoC® 5LP Prototyping Kit

I’ve been on the hunt myself. You get what you pay for. Three digit “beginner boards” have everything under the sun. They’re more like R&D sample boards. Two digits have just a bare FPGA and minimum supporting hardware.

Finding a middle ground (preferably for less than $100) with supporting documents is what I’ve been looking for. To get rid of the “did I build the circuit right?” Inherient with barebone boards and avoid the “I spent a shitload of money on this board so I’ll stay with it even though it sucks” with the insanely decedent boards.

This board looks very nice since I know the AVR series already. Just wish it didn’t have that awful footprint.

Another problem I found is, what is the “right” number of cells to play with? I’m still hazy on how to figure that out.

The problem here is that Altera and Xilinx use different words.

I first bought a Spartan 3A. I think it was 200,000 gates. I don’t know what that is in logic elements, it could be 2,000 or it could be 20,000 who knows.

Then I bough a Spartan 3E that had 500,000 gates.

Then I turned to CPLD and bought – Xilinx 36 LE’s, 72 LE’s, then Altera 240 LE’s , 470LE’s

Absolutely huge difference. I did more in the smaller CPLDs than I did in FPGA that probably had thousands times more capacity.

As a starter any FPGA is probably going to be thousands times bigger that you need. It’s only when you have advanced a lot that you could use the full capacity.

The configurable logic block, memory sizes etc are more realistic of the usable FPGA/CPLD resources as they are under your control. I always ignore the gate count. They are only useful if you are using it for MTBF type of calculations or impress people.

From what I hear, “gate” counts are like comparing mattresses, manufacturers use different ways of expressing it, specifically to confuse you and make direct comparison impossible. It would be nice for someone to collate a list of lots of projects, done by different people, and how many gates each one used. In Xilinx / Altera / Lattice “gates” for each one. Or “blocks”, or whatever, but something comparable. Then you’d have a rough guide for what’s needed for a project of a particular complexity.

I suppose otherwise the rule of thumb is the one that applies to most things. Price. MRP per 10,000 units or whatever. A more expensive one is generally gonna do more. You don’t have to buy 10,000 of course, but MRP gets past the various discounts and whatever other variations that retail price would have. It’s a VERY rough rule of thumb, but it tells you something.

I found most of the configurable blocks are pretty similar from the major players these days. There could be an advantage of one architecture over the other, but certainly not going to be more than tens of %. The part that is much harder to evaluate is the routing resources and how well the software does the routing/optimization. That part makes a heck of a difference as how full your FPGA can be.

I made the mistake of assuming the complexity of my CPLD to committing into a package for my very tight layout. It turn out that the design uses a lot more routing resources than less than half filled macrocells. I was already using the highest density part in the package. So make sure you have an upgrade path. In my case the CPLD is tied to a FPGA, so it isn’t a total failure.

@[Greenaum]

I get it Xilinix use “logic” gate and Altera uses “apple” gates and soe others use “dildo” gates.

A gate is a gate you idiot and a gate count is exactly that.

Xilinx and Altera confuse the parameters by using different combinations of “logic element” “logic units” and “macro cells” all of which are many many gates.

No, a gate isn’t “a gate”. FPGAs contain a collection of resources. You can’t just count the number of effective gates for comparison, just like you can’t measure a CPU’s performance by looking at its clock speed.

To get a true idea of the resources available on an FPGA you need to know: the number of LUTs (or 4 input equivalents), the number of flip flops, the amount of block/MRAM on chip, the number of DSP blocks (how many multipliers in particular), the number of clock generators/networks etc. Xilinx have moved away from quoting their FPGAs in gates because of this. They’re the market leader so had no need to do this for marketing reasons.

@[Sweeney]

“No, a gate isn’t ‘a gate’. FPGAs contain a collection of resources. You can’t just count the number of effective gates for comparison”

You haven’t worked with older Xilinx like the Spartan 3 – 200, or Spartan 3 – 500. The 200 and 500 refer to 200,000 gates and 500,000 gates.

No one said gate count was a useful metric.

I was reffering to this – “From what I hear, “gate” counts are like comparing mattresses, manufacturers use different ways of expressing it”

It’s not like the most basic units of logic can be express by other metrics.

Then you talk of LUT’s (logic units). Are you sure you don’t mean LE’s (logic elements) they are quite different.

These confusing terms are no accident. Xilinx and Alterra don’t want you to cross-compare products.

No, I definitely meant LUTs. They are the basic building blocks of LEs, along with flip flops. The number of LUTs in an LE varies from manufacturer to manufacturer and model to model. Xilinx confuse things further by talking about slices, but the LUT is still the base unit.

I disagree with a number of people on this one but here goes –

Want to learn to drive – take this 1500 Cubic Inch Funny Car – 6.4 seconds on the quarter mile – 9 gazillion horse power and nitrous oxide injection – you will never need anything more !!!!!

That argument is crap. Just like “No one will ever need more than 640kBytes RAM”

Also you’re not going to know what suites your (long term) needs down the track until you go down the track and learn HDL.

So here is what you need to know.

1) You need tutorials unless you are already so good at VHDL that you have written a simulator in the computer language “Brain Fuck”

2) About the hardware – see number 1)

Q: What do I buy.

A: It doesn’t matter what it is as long as it has good tutorials.

Q: How much will it cost

A1) About $150 for the programmer, another $450 for that latest and greatest development board with all the flash bling features that you will never understand before you give up and $27,000 for a tutor because there are no tutorials for that specific and complex board.

A2) Get the Atera Web kit (free). An Altera JTAG programmer ($5 on ebay). Some cheep CPLD breakout board (With a crystal) if you are OK to add hardware parts youself or a cheep CPLD/FPGA development board with a couple of switches, LEDs, 7 segment displays and simple stuff like that for (usually) under $50 and go with generic online tutorials.

What I did.

My first purchase was a GameDuino (Xilinx Spartan 3A) – some where between $40 – $100. I decided on this because I could use it even if I didn’t end up learning VHDL with it. It had no VHDL tutorials, it was very purpose manufactured and there was no hope of me learning VHDL with it.

My second purchase was a Papilio one with a LogicStart MegaWing. It has a tutorial that was written for it but the tutorial wasn’t good and I really struggled with using Xilinx IDE. The LogicStart MegaWing was excellent and so to was the supporting documentation.

My next purchase was a Altera CPLD breakout board (with crystal) and Altera programmer. I then struggled with the differences between the Alter IDE and Xilinx IDE.

Then I downloaded a trial VHDL editor called Sigasi. The text highlighting in Xilinx is a joke. In Altera it’s a bit better but it’s still just text highlighting. Sigasi will show many errors “as you type” your HDL unlike the others that only show errors when you compile and then you have little clue what they mean – Xilinx is the worst for cryptic errors.

And Hallelujah I could actually “get it”. After that I went back to Altera CPLD – Xilinx CPLD and the Papilio One as a part of the learning experience. Then I went free range lol.

Some tips –

Aletra is not very intuitive when it come to originally setting up a project – watch some Youtubes that have high enough resolution to see what is being done. Altera pin constraints is a pain to, I am still looking for a better for that.

Xilinx takes the grand award for connecting their “warning” system up to a 1024 bit Linear Feedback Shift Register. What does that mean … option 1) – spend several hours combing the forums for the meaning of a “warning message” only to find out that no-one is really sure … option 2) Ignore all warning messages unless they break through the screen and start spawning.

Both of these IDE’s are a collection of sub function programs that run in the background under the control of the IDE. The IDE doesn’t often report the *context* (what was being done at the time) of an ERROR so it makes it very hard to understand. For ERRORs hit for forums. Altera is better than Xilinx in this regard (IMHO). Xilinx will come up with cryptic errors like Babel Fish cannot be acceding at zero.

Anyway, when you’ve done all this – you *WILL* be able to choose the hardware that best suits your needs without spending hundreds of dollars on features that you wont understand or want.

PS: If your buying something to learn on that has RAM than make sure it IS SRAM and *NOT* SD-RAM.

Hey thanks for the info, I think I am going to give an Altera a go. I found this on ebay http://www.ebay.co.uk/itm/Altera-Cyclone-NIOS-II-FPGA-Board-EP2C8Q208C8N-USB-Blaster-JTAG-programmer-/261815907877?hash=item3cf571b625:g:UjAAAOxy3zNSlfiF

It’s in m price range and looks like it’ mean’t as a beginner training board. would you think this would be a good start?

It’s probably not the best start as it doesn’t have the switches and LEDs that everyone should starts with.

The LCD isn’t useful until you code in a CPU so that’s not a beginner thing.

I will go poke around ebay.

cool thanks!

I think “NIOS” in the name implies it’s based around someone putting a soft-CPU in there. But yeah that’s running before you can walk. Meant for people who are specifically wanting to do CPU, NIOS, stuff I suppose.

@[Greenaum]

Right and people just starting out in FPGA what to start by writing a soft CPU.

Idiot!

There is a cheaper one here – http://www.ebay.co.uk/itm/FPGA-Cyclone-Altera-FPGA-EP1C3T144-Development-Learning-Board-/251506876532

but it doesn’t have PS2 or VGA *RAM.

The one you have chosen lack some of the very basic stuff that you would start with. Good it has 6 LEDs but it looks like a very small number of switches.

However given the lack of options that I see on that particular ebay location what you have chosen is perhaps the best choice.

The I/O I had to start with were –

http://www.gadgetfactory.net/images/logicstartmegawing/tn_LogicStart_MegaWing_Top_white.jpg

It had switches LED’s 7 segments displays, D to A audio output, VGA

I missed this reply sorry. Thanks for going to the trouble of helping me, I’m gonna give this one a go and buy it.

What’s wrong with using my board? :-(

Your board could be great, it could be shit … who knows?

I couldn’t be bothered downloading collections of information to make any assessment because I’m not a beginner and so I probably would be buying it anyway.

Just guessing by the scant information that I can see without downloading, I would suspect it lacks documentation so I won’t be recommending it.

I just didn’t want to buy a board that was only for use with Ardunio IDE as when I advance on to doing things myself it would restrict me. Not that I have anything against Arduino I love them.

but I have now read your website and realised that it is not just Ardunio based, I think I will be ordering one of yours. I like the idea you have a few example programs on there, this is just what I am looking for. I will be ordering soon hopefully middle Dec. I have bookmarked your page.

Thanks for commenting or I may not have ever realised that.

Thankyou Jack for giving my board a 2nd look :-) To be sure, my FleaFPGA Uno board is definitely NOT your everyday run-of-the-mill Uno.. :-) Cheers.

No probs I look forward to giving it ago. I have been toying with the idea of trying for a while now time to take the plunge. It’s just a bit hard trying to find a starting point when ever you try something new. It always seems hard until you get an LED blinking.

It’s very easy to break away from the Arduino IDE. I actually use vim and make for my Arduino stuff. Also there’s nothing stopping you from writing regular C/C++ code and just using the Arduino downloader to get it on there. I had to do some PWM stuff that wasn’t supported in the sketch code and I ended up just ditching all the sketch stuff and rolling my own. This way an project can be as simple or as complex as it needs to be.

There is nothing wrong with your board, it’s actually quite nice. if there is a quibble it is in regards to your target audience.

It’s certainly not for the beginner given the lack of progressive tutorials to take a noob from turning on a LED to say doing a simple state machine or up and down counters. If you want to aim your board at this market, you’ll need to put together a package of tutorials to help the noobs interested in this field IMO.

But for the customer who is used to mucking about with CPLD’s and FPGA’s, it’s fine.

@zerg Thanks for your feedback.

I agree with you. My FleaFPGA Uno User Manual is available and geared towards use as a general purpose FPGA dev board. I wanted to make that available (along with a few solid examples) as a minimum. You may note I have also recommended several VHDL reference texts as well as links to 3rd party sites with coding examples on my project page. Ultimately however, I would like see our own progressive tutorials in place on fleasystems.com. I do have a large collection of personal HDL examples (many need some ‘tidying up’ first tho.. :-) as well as existing uploaded examples for my older FPGA dev. board that could be used for it.

For the immediate term, my focus is on the Arduino-compatible aspect (of which completing a compatible 3.3V I/O shield listing is one to-do task). Currently all FleaFPGA Uno boards are shipped with the F32c SoC soft-CPU installed in the FPGA. Until I write a separate how-to on using my board as an F32c-powered machine, instructions on setting up the IDE as well as a suitable IDE plugin+sketch examples download link etc. are currently sent via email in the interim.

Cheers Valentin

What I started with was a Pappilio, a couple of years ago. The basic model, not the arcade or pro or whatever they call it now. No, it doesn’t have switches and LEDs and I/O ports on the board; I didn’t need those because I have a breadboard and a bunch of switches, LEDs, and sockets scavenged from any electronic that has died in my vicinity since I learned to solder. Were I to be looking for one now, this looks like a good starter. Always remember, the Arduino doesn’t need to be programmed in the Arduino IDE.

Now, if you don’t have a breadboard and a parts bin, or don’t like using those, then a full dev board is the way to go. You might get the benefit of HDMI output to a monitor if that’s your fancy, something that’s not easy via breadboard.

I’m new to FPGAs and curious– what are they good for that a regular microcontroller can’t do?

I’m new too but my understanding is imagine you have a chip with lots of circuits inside that are not connected or doing anything, You use software to tell the chip which circuits you want connected and active. So you can program the chip to function as another chip or multiple chips or as a complete custom package. It’s like designing a chip for a specific job without having to go to a manufacturer and saying I want you too design and produce me a chip that does X,Y,Z.

If I got anything wrong I am sure someone will tell you what I said wrong but this is my understanding. If you are looking to get into FPGA I am going to buy the one posted here it looks great for beginners.

FPGA – you get to design your own hardware. It can do stupidly simple thing really really fast. Multiple things can happen in parallel.

Software – you can do a lot more complicated things, but one at a time.

FPGA is the modern and most complex of a series of chips that went from Gate Array Logic (GAL), Programmable Array Logic (PAL), Simple Programmable Logic Device (SPLD), Complex Programmable Logic Device (CPLD) to Field Programmable Logic Device (FPGA).

FPGA is different in that it has to read it’s configuration from a ROM or flash chip when it powers up. Other chips stay configured when powered off.

FPGA’s have basic logic functions like the 74xx chips like NAND gates, OR gates and inverters. They also have logic cells or macro cells that can be configured as one of the many forms of Flip-Flop. The Flip-Flop or Register is the basic unit of single bit memory that it used for tasks or functions that cannot simply be done with simple gates.

You program the connections inside the device so that it “is” what you want it to be. In a modern FPGA there are literally tens of thousands of these logic blocks so you can code in a CPU, some RAM and even an entire computer system.

Modern FPGA also has features such as large amounts BLOCK RAM, frequency synthesis for generating specific frequencies from a fixed external crystal.

Making a CPU in a FPGA chip is less efficient by way of cost, complexity and power consumption when compared to a real CPU so now some FPGA include a hardware CPU built-in.

These chips were once expensive but are now much cheaper and accessible to the hobbiest.

Now the entry barriers are learning VHDL / Verilog which is not that difficult and the harder part of learning to use a propriety development environment.

The disadvantage of FPGA is higher power consumption. Normal IC’s (ASICs) use far less power for a specific function.

The advantages are customisation. And low chip count costs when compared to (ASIC).

The nature of the programming language and chip design also allows very high levels of parallel data throughput or analysis without the use of a CPU. High signal or data processing power without anything that could be called a (conventional) processor.

To Richard Baguley:

Many thanks for your concise and well-written article around my FleaFPGA Uno hobby project. This part-time hobbyist and casual hacker is eternally grateful. :-)

Sincerely,

Valentin Angelovski

@Valentin: it’s pretty obvious you’ve put an phenomenal amount of work into this and you appear to be selling at cost. Just curious what your driver is. Looks like you have a skill set that could be earning you megabucks at any latency oriented prop trading shop for instance.

@nes: Thanks for your comments and also for your question. I originally designed my board for myself as well as a few close friends within the hackerspace community to play with. However, it turned out to be (arguably) cooler than I’d originally thought it might be, so I decided to submit my project HaD to gauge wider interest. I guess this is where we are currently.. :-)

If there’s little/no interest, I will simply ship the current pre-production batch of boards until all gone and decide then what I will do next. All options are on the table. Anyways, we’ll see how things go. :-)

Not sure if prop trading would be my thing :-) I’d rather be working in the electronics industry again but that isn’t going to happen anytime soon. Cheers.

I’ve needed an excuse to learn the open Lattice tool chain, so if you haven’t sold out by the time I finish moving I’ll be ordering one.

@Quin No worries. Feel free to drop me an email or PM when you’re ready.

Will likely run out of preproduction boards by tomorrow, so I may have to decide quickly what I am going to do next..

In the event that I do get caught out between production runs, you could always try twisting my arm for some hand-assembled older rev. D (i.e. almost same as rev. E but without the minor incremental fixes or cosmetic mods etc.) boards as I have around a dozen or so Rev. D bare PCBs on hand. Cheers Valentin

Am I the only one here that read it as “Flea FP Guano”?

You are. I read it as f-leaf p-guano. Perhaps some extract from a scientific review of fertilisers.

F Leaf PGA… Some new golf Tournament?

New IC package type?