At the Linley Processor Conference today, SiFive, the semiconductor company building chips around the Open RISC-V instruction set has announced the availability of a quadcore processor that runs Linux. We’ve seen RISC-V implementations before, and SiFive has already released silicon-based on the RISC-V ISA. These implementations are rather small, though, and this is the first implementation designed for more than simple embedded devices.

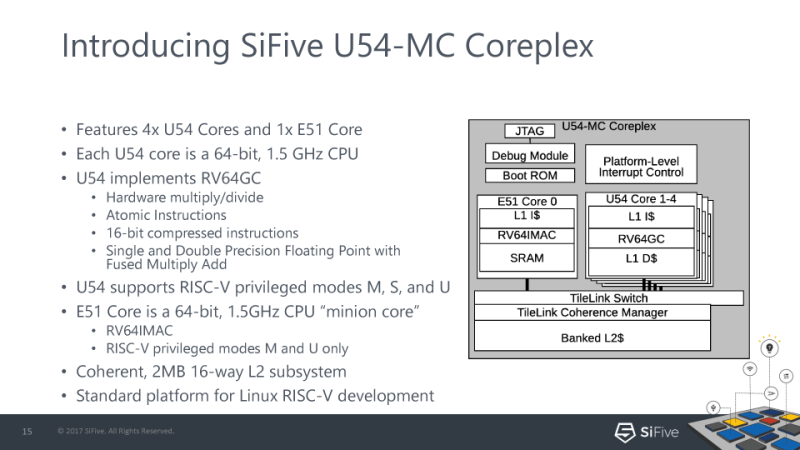

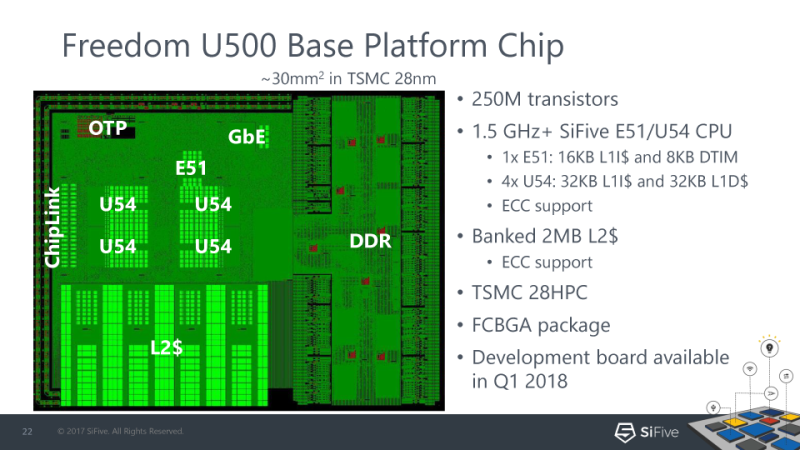

This announcement introduces the SiFive U54-MC Coreplex, a true System on Chip that includes four 64-bit CPUs running at 1.5 GHz. This SoC is built with TSMC’s 28 nm process, and fits on a die about 30 mm². Availability will be on a development board sometime in early 2018, and if our expectations match the reality of SiFive’s previous offerings, you’ll be able to buy this Open SoC as a BGA package some months after that.

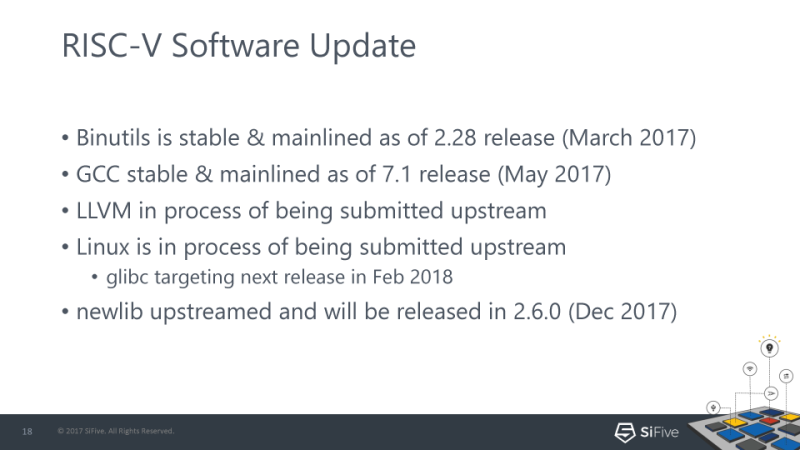

So far, there are few tangible details about the SiFive U54-MC, but what we do know looks great. On the software support front, RISC-V support in GCC is stable and mainlined as of the 7.1 release. LLVM is in the process of being submitted, and Linux support is getting there too. Considering no one outside SiFive has this hardware in hand, this is just fine.

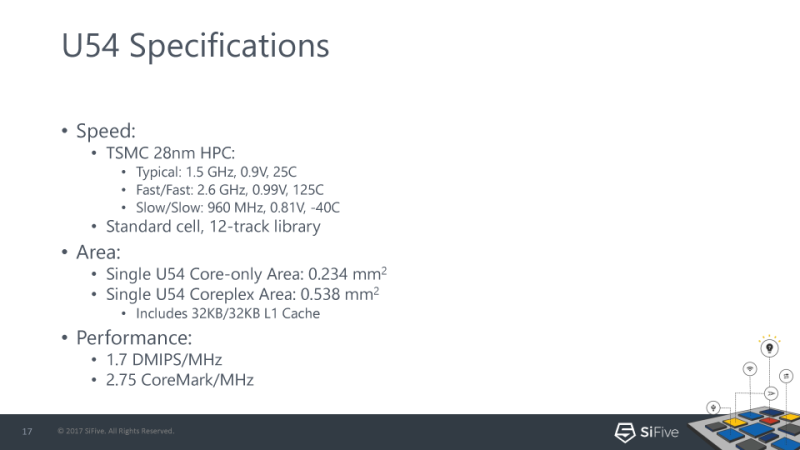

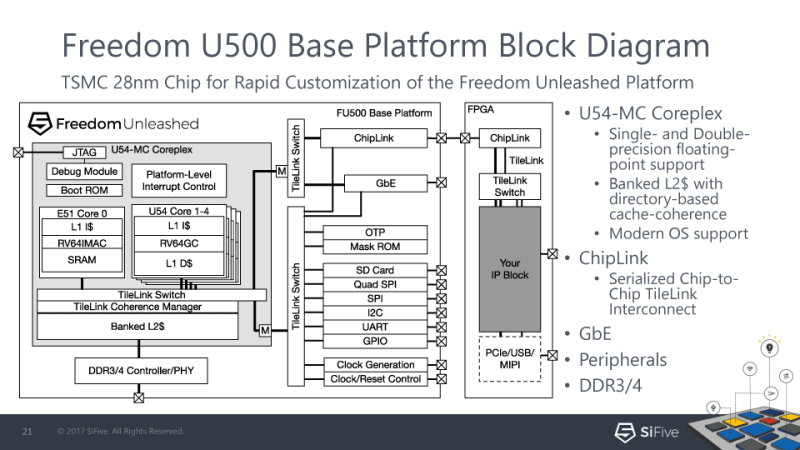

The hardware part of this SoC is where things get interesting. This is a truly modern SoC built with a modern process. Typical performance is 1.5 GHz, with 1.7 DMIPS/MHz and 2.75 CoreMark/MHz. Peripherals included in this SoC include a DDR3/4 controller, Gigabit Ethernet, SD card, SPI, UARTs, and the other usual peripherals found in every other processor. Of special interest is the ChipLink interconnect. This is a direct connection to an FPGA where IP blocks run, giving the SoC peripherals like PCIe, USB, MIPI, or other high-speed interfaces.

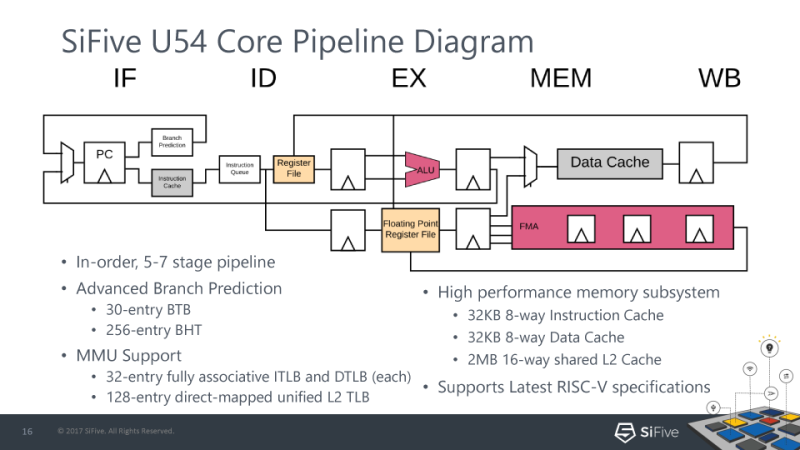

Below you can check out a few of the relevant slides from SiFive’s announcement today:

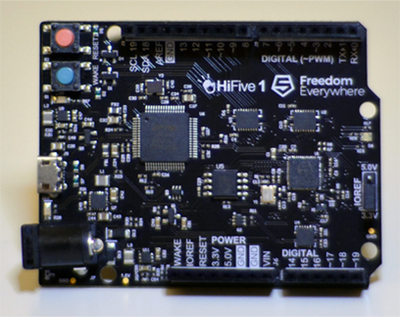

We’ve taken a look at SiFive’s RISC-V offerings in the past, most notably in the form of the HiFive I, an Arduino-shaped board loaded up with the SiFive E31 CPU. This is a microcontroller, and a far cry from a quadcore SoC. However, the E31 is a remarkable microcontroller that’s exceptionally fast, capable, and has a surprising amount of support and tutorials behind it. Right now, if you want a microcontroller that’s exceptionally fast, has fast DMA, and can control a ton of WS2812 RGB LEDs, your best options are a Teensy or a BeagleBoard with the fantastic PRUs. The E31 is a contender, though, and with recent, lower cost offerings like the LoFive we’re expecting RISC-V microcontrollers popping up in some very interesting projects soon.

This announcement is just that — an announcement — and our expectations are tempered by the fact that our desire for instant gratification is not satiated right now. SiFive has been doing a lot of work over the past few years, though, and given the release of the HiFive 1, their work in getting trays of their E31 microcontrollers into the hands of engineers, and their honestly fantastic work on their own support forums, there’s no reason to expect this Open SoC is vaporware.

Modern? 28nm is so 4 years ago…. I’d call it “mature” maybe.

Except now it is just another proprietary closed thing with poor software ecosystem. I see no benefits of picking this over ARM as a standalone device. It may be different for people that licensed IP to build their own SoCs, of course. But for general public, this is not a very interesting offer.

That depends on what kind of people “general public” refers to. I would say for general public in the general meaning, products like single board computers are not interesting.

The main question is if open source hardware matters. In order for people to start developing the software ecosystem itself, hardware like this is definitely important and interesting.

Hi Alex, true! In fact OpenSPARC T1 is more open-source than SiFive’s RISC-V. But because they are developing RISC-V CPU/SoC other companies could start to do the same and release its hardware description language as well.

I doubt market will support this. There is very little actual value in having open source HDL for a real SoC done in hardware.

All I personally want from RISC-V guys is to produce binaries for their tools. Building things from scratch is cool and all, but it is slow and error prone.

They need a differentiator: price, performance, tools, integration, etc.

Something like RISC+FPGA…..

wait that’s exactly what they have.

Now you have my attention.

They don’t have an actual FPGA inside the device. And you can connect FPGA to any MPU already. Plus you can get Zynq.

And I bet they can’t beat Zynq on price.

I must clarify “beat” in a combination U54 + FPGA. U54 alone may be cheaper, of course.

epiphany

1.7 DMIPS/MHz is slightly lower than an ARM Cortex-A7, so it’s not quite as high-performance compared to the competition, but for a first linux Risc-V chip, it’s certainly encouraging!

That’s why they compare their stuff with cortex A35 (1.78 DMIPS/MHZ) and not with Cortex-A72 (4.72 DMIPS/MHZ) or Cortex-A73 (~6.35 DMIPS/MHZ)

There are several other things needed to outperform existing products on the market, not just a new ISA. If it’s lacking some really cool extra feature, like super low power consumption, super fast context switch (ex. for handling interrupts or thread switch in os),reprogramable logic (ala FPGA) etc. ,than it won’t be successful.

Also target some market, there isn’t single solution for all. Like Power or performance. Like cortex M and cortex A. Even in cortex A they have the in-order power optimized cores and the out-of-order performance optimized cores.

RISC ISAs are nice, and I really like them, but to be honest with contemporary instruction fetch and decode (ex. recoding into smaller instructions and refuse them for faster processing) techniques the optimal solution is between CISC and RISC. CISC compress the instruction stream. Smaller code size, more instructions in cache, faster execution etc. etc.

Just a basic example:

Try to load an immediate into some register. on x86_64

(gcc syntax)

movq $ 0x123456789abcdef0, %rdi

on RISC ISAs the same operation is one additional load (if PC relative instructions are supported) or several instructions (depending on the size of the constant) Both solutions are at least 4-10 times slower (in clock cycles) than the x86_64.

And there are several other examples. I understand that they started designing this RISC-V architecture in the times when RISC appeared to be the solution, and designing a RISC ISA is easier than making a complex CISC decoder.

ISA doesn’t matter that much nowadays. 99.999% of the users will use some kind of compiler for the 99.999% of the time (so compiler optimization really matters, and a well polished compiler optimizer for a give architecture takes years (5-10+))

IF it’s open source, it can definitely turn out to be the cheapest SoC after some time, due to inter-competition between various chip makers. In similar way that ARM Cortex-M microcontroller became cheaper than PIC yet offering high performance and featureful because hundreds of chip makers were making same Cortex-M thing.

They already said it is not going to be open at all. They “pivoted”, I guess.

Where did they say that?

In some interview after they’ve got $8.5 million round of financing. I can’t find a link at the moment.

Basically all the stuff based on RocketChip (FE310 really) will be frozen, and they will switch to a model of providing IP for money. But to do that, they would have to keep the code closed.

It’s not, they drop opensource in august, not updating their git since (be sure to clone it before they wipe it).

oh, crap, looks like i have to port our open source graphics accelerator to this new chip ;)

https://hackaday.com/tag/orsoc/

the hard part would be to find the time.. i am sure i had some laying around a few seconds ago…

Ok this is pure awesome, now i can play around with new hardware without buying new hardware :D

Free evaluation:

FPGA Bitstream

Get immediate and free access to an FPGA bitstream featuring a fully functional Coreplex with system peripherals. Benchmark and run your code immediately using commercial or open-source RISC-V tools.

High Performance — 65MHz emulation

Multiple Coreplex IP bitstreams immediately available

Upload your own programs using the Freedom E SDK

Compatible with the $99 Artix-7 Arty Evaluation Kit

Evaluation RTL

Ready to synthesize RTL in your environment? Want to run Coreplex IP through your tool flow for a full evaluation? We make it simple. DocuSign our evaluation agreement and receive fully functional, synthesizable Verilog RTL instantly.

Fully functional, synthesizable RTL

Run it in your own simulator

Simple, no-cost evaluation license

Painlessly upgrade to a full license

Yeah if you have $500+ Altera board. That thing is a resource monster.

Notice they don’t even say up front how much it gobbles up.in terms of FPGA resources.

It does not matter. FPGA part is just for simulation and development. At 65 MHz it will be painfully slow and not fun, something you will only do if this was your job.

I think you missed the:

“Compatible with the $99 Artix-7 Arty Evaluation Kit”

The SiFive project went pear shaped when they invited members, large corporations signed up as members and the first thing they do is introduce commercial licensing. Now they have dropped the open source idea completely. Instead of being a game changer it has become nothing more than an ARM alternative for a group of large silicon manufacturers. We will have to live with the decisions made by the members, inevitably they will be commercial decisions rather than new ideas and innovation being fed into an open project. I had great hopes for RiscV but it looks like commercial interests have taken over and ruined it.

I didn’t quite understand your point. SiFive is a private company, so has no “members”. There is no such thing as “SiFive project”.

SiFive decided to open their first architecture (which was derived from UCB rocket project), but stops offering it as pure opensource after a while, because they need to earn some money.

RISC-V foundation has members (compagnies, universities and even private members if you want), SiFive is one of the members of RISC-V foundation.

Opensource licensing from RISC-V is quite permissive, but hey, it comes from UCB which created BSD license, so don’t expect any GNUism here.

That’s also why RISC-V got so much traction in the semiconductor industry, it’s free from GNUism (which is banned in every company I have been) and members can contribute and drive the RISC-V future.

CPU design and production costs a lot of money, in particular in the high performance area. It is unrealistic to expect SiFive to release its R5 quad core source code with GNU license.

If you want a truly open source cpu then you should want an open FPGA solution so that anybody can build his own cpu. AFAIK there is only one open FPGA tool chain, and that is iceStorm [1] for the proprietary Lattice iCE40 FPGA. I wish we had an open FPGA chip AND open toolchain. That would be really interesting!

[1] http://www.clifford.at/icestorm/

It is unrealistic indeed. But that’s exactly what they promised originally. And that’s exactly why people were excited about it.

At this current state, they are no different that a dozen other IP providers with proprietary cores. And those providers have established reputation and markets.

I don’t know the details of this closing of RISC-V’s source that so many mention here. If this has happened then instead of complaining why not just fork from the last open release and go from there?

This is not really a closing. They have a completely different design for this chip that they made in-house. There is no need to clone the original one, since it was derived from RocketChip, and RocketChip continues to be open, of course.

RISC-V is an ISA, not an implementation. There are lots of *implementations* of RISC-V, some are open, others are not. RISC-V is as open as it’s always been. SiFive’s implementation is partially open, in the sense that it’s based on Rocket Chip which is hosted by Freedom Chips (project https://github.com/freechipsproject/rocket-chip), but as we all know there’s a lot more to an actual physical microprocessor and much of that isn’t open (or free).

Sifive ?

Oh yes: Sharknadove !

Back to looking up for http://www.lowrisc.org/ then…

s/Athe/At the/

Thanks!