A flip-flop is one of the most basic digital electronic circuits. It can most easily be built from just two transistors, although they can and have been built out of vacuum tubes, NAND and NOR gates, and Minecraft redstone. Conventional wisdom says you can’t build a flip-flop with just one transistor, but here we are. [roelh] has built a flip-flop circuit using only one transistor and some bizarre logic that’s been slowly developing over on hackaday.io.

[roelh]’s single transistor flip-flop is heavily inspired by a few of the strange logic projects we’ve seen over the years. The weirdest, by far, is [Ted Yapo]’s Diode Clock, a digital clock made with diode-diode logic. This is the large-scale proof of concept for the unique family of logic circuits [Ted] came up with that only uses bog-standard diodes to construct arbitrary digital logic.

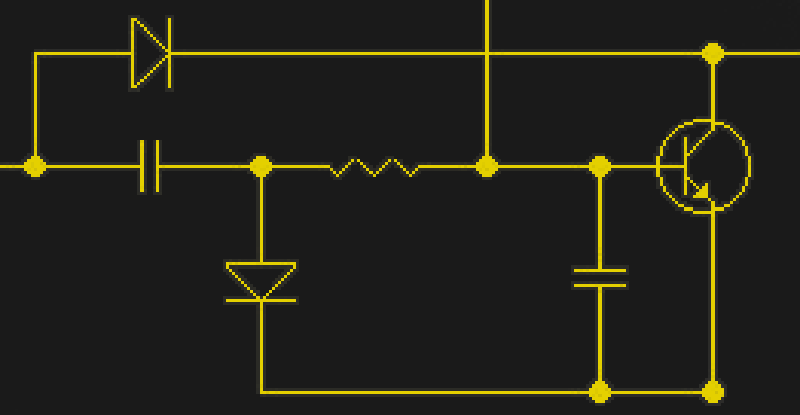

The single-transistor flip-flop works just like any other flip-flop — there are set and reset pulses, and a feedback loop to keep the whatever state the output is in alive. The key difference here is the addition of a clock signal. This clock, along with a few capacitors and a pair of diodes, give this single transistor the ability to store a single bit of information, just like any other flip-flop.

This is, without a doubt, a really, really weird circuit but falls well into territory that is easily understood despite being completely unfamiliar. The key question here is, ‘why?’. [roelh] says this could be used for homebrew CPUs, although this circuit is trading two transistors for a single transistor, two diodes, and a few more support components. For vacuum tube-based computation, this could be a very interesting idea that someone at IBM in the 40s had, then forgot to write down. Either way, it’s a clever application of diodes and an amazing expression of the creativity that can be found on a breadboard.

“Either way, it’s a clever application of diodes and an amazing expression of the creativity that can be found on a breadboard.”

Weird as using the very properties of a board as part of the function.

The real question is performance : surface, cost, speed and energy…

Plus apparently you need a refresh clock.

Yawn, Would you rather this was Conventional-a-Day? ;)

Kinda vaguely reminds me of the MoSys 1T-SRAM used on the Nintendo GameCube and Wii systems. Those used a single transistor per bit, but had DRAM like refreshing integrated into the chip. The chips got density closer to DRAM, and speeds closer to SRAM out of the configuration.

Very cool!

Slightly related, I found that you can get a single MOSFET to act as a latch with a bit of tinkering with magnets – maybe someone can explain what I saw? I wonder if it might be similar to the concept behind MRAM, but I’m hopelessly out of my depth. It might just be a weird pin capacitance/inductance thing caused by a ridiculously oversized FET.

Step 1: attach the 3 pins of your MOSFET to magnets – I used big TO-220 FETs with very low on resistance, which might matter. You can solder to nickel-plated NdB magnets if you’re careful and quick, or use an electrically-conductive epoxy.

Step 2: stick those magnets to a piece of ferrous metal, and bend the leads if necessary to make the case lie flat against the metal. Dry-erase boards work well because the paint provides electrical insulation so the pins don’t short.

Step 3: Use the MOSFET normally as a switch. Observe that its gate seems to latch even after power is removed from the whole circuit. I’ve left them unpowered on a whiteboard for days and come back to the same ‘on/off’ state when connecting a battery across the source pin and load “+”.

Isn’t that weird? I’ve tried it with both P-Ch ‘IPP80P03P4’ FETs and N-Ch ‘PSMN022’ ones, but I haven’t had the time to look more deeply into it.

Oh, but be careful if you try to solder to magnets – the tip will often be attracted to the magnet poles, which can lead to a bit of a mess.

“Aw Snap!”

Are there non ferrous soldering tips?

You could just hold it to the iron until it reaches its curie point

A mosfet will latch with out the use of any magnets I often use the property to test Mosfets.

With the device out of circuit connect multimeter probes to Gate and Source. For an N chnl neg to gate pos to source -this charges the internal capacitance of the gate. The MOSFET will now be in a conductive state from S – D. To turn the MOSFET off short the gate to the source.

As I only use this property to test the opperation of MOSFET I haven’t looked at how long it will stay on for or how much current can be switched.

Indeed, this is the basic property that Flash memory exploits: the gate forms a capacitor with the channel. With no connection to the gate, the self-discharge rate is extremely low, so a disconnected MOSFET will tend to stay in the same state it was last in for a considerable length of time. Flash chips use MOSFETs that are engineered to keep the charge for an even longer time than most standard FETs, but other than that the basic premise is essentially the same.

What you are experiencing i suspect is static chargeing the gate capacitor.

That’s a discrete one bit DRAM.

Mmmm, two diodes and a few capacitors. Looks like a reverse engineered transistor.

+1

*touches finger to nose*

Yup. This is obviously a “one-transistor” circuit in only the most literal sense. I’m disappointed with HaD on this one.

It reminds me of a flash memory cell, so not so weird or completely unfamiliar. There are plenty of free electrical engineering study sources on the web, I suggest that people make the most of them. You can make such a toggle from almost anything, even a seat in a park and an apple, benchon, benchoff, benchon, benchoff…

Isn’t this essentially what everyday dynamic ram (dram) chips use? The bit of the circuit actually storing the state are the capacitances in the circuit. A refresh pulse every few ms (or ns) is needed to keep state. https://en.wikipedia.org/wiki/Dynamic_random-access_memory

Exactly my thought when looking at the circuit description. A flip-flop should hold a steady state in static conditions and not need a refresh clock. He built a single-cell Dynamic RAM.

I agree. I had the same thought. Now if they got rid of the refresh clock….. I have some old core memory kicking around (8k or 16K x 8 I think, the old DEC boards). I wonder how many transistors it took to access a cell of that? Time to wiki…

This is a clever circuit! It reminds me of a 1-transistor bistable in a 1960’s GE transistor manual. That circuit was wired as an oscillator, with the base bias AC-coupled and rectified from the collector waveform. It had two states:

1. Oscillating: The output AC biased the base to keep it oscillating.

2. Not Oscillating: Transistor off, so no oscillation, so no base bias.

Momentarily biasing the base low stopped the oscillator. Momentarily biasing it high started it again.

I claim exception under the rules of homeomorphism! A transistor + two diodes = two transistors.

The diodes in the circuit aren’t arranged like the diodes in a transistor though. A BJT’s base is either a common anode or a common cathode. Version 1 of the circuit has the diodes in series, and version 2 puts a capacitor between them.

To me, the first version looks like an RTL, with addition of diodes.

The second one has diodes arranged like in an NPN transistor, with (yes) capacitor in between.

So nice to tinker, but not improving on anything..

You can’t make a transistor out of two diodes, though. Even though you can use a transistor as two diodes.

True. I’m just making a comparison of complexity of all the parts.

With the clock, capacitor and transistor it makes me think of a degenerate 1-cell bucket-brigade device. (BBD). I wonder if those diodes can be used to perpetually refresh a multi-cell BBD and suddenly you have a small storage device that is no harder to access than magnetic drum storage or mercury delay line but way more compact.

So it’s sorta RTL? With diodes and caps thrown in?

This is where a unijunction transistor makes more sense.

That’s the first time I’ve ever heard anyone say that a unijunction transistor makes any sense! :)

A Unijunction Transistor makes sense when used as a multivibrator. There, now you have two examples. There are more.

i wish the article had clarified that the clock is refresh, and not signal. would have saved me from trying to decipher DRAM.

Will this make a smaller SRAM standard cell, using the same technique used in building DRAM cells? If so, will we start to see decrease costs and increase capacity of SRAM chips from DRAM manufacturers.

It seemed to me that this kind of memory cell, if converted to CMOS, consumes more power than standard low power SRAM, but it should not exceed the power consumption of standard low power DRAM since there is no periodic refresh involved.

If this type of SRAM cell becomes viable, we might see a paradigm shift in computer memory configuration.

The problem here is that it has none of the advantages of SRAM: it’s slow because it needs to charge a capacitor to change state rather than just switching a transistor, and it needs a refresh circuit so isn’t simple to use like SRAM. Basically, it’s a single bit DRAM with a clever arrangement for the refresh circuit that makes it smaller (but can’t easily be shared between multiple rows so wouldn’t be useful for larger DRAM designs).

Very nice!

I was looking for a flip flop with the least number of transistors and Uncle Duck suggested this to me.