It is no secret that we like the Lattice iCE40 FPGA. It has a cheap development board and an open source toolchain, so it is an easy way to get started developing low-cost, low-power FPGA designs. There are a few members of the family that have similar characteristics including the top-of-the-line UltraPlus. [Steve] from Lattice and [Michael Klopfer] from the University of California Irvine have a three-part video series that explain the architecture of the devices. Altogether, the videos are about an hour long and — of course — they use the official tools, not IceStorm. But it is still a great time investment if you have an iCE40 board and you want to understand what the chip has under the hood.

The first part is fairly short and talks a lot about applications. There’s also a nod to the hobbyist use of FPGAs. Keep in mind that the iCE40 FPGAs come in different sizes and variants, so don’t get excited when you see them mention a RISC-V — that isn’t going to fit in your iCEStick, that we know of. The iCEstick has a HX-1K onboard, which is the high-performance variant with 1,280 logic elements, as opposed to the low-power (LP) version.

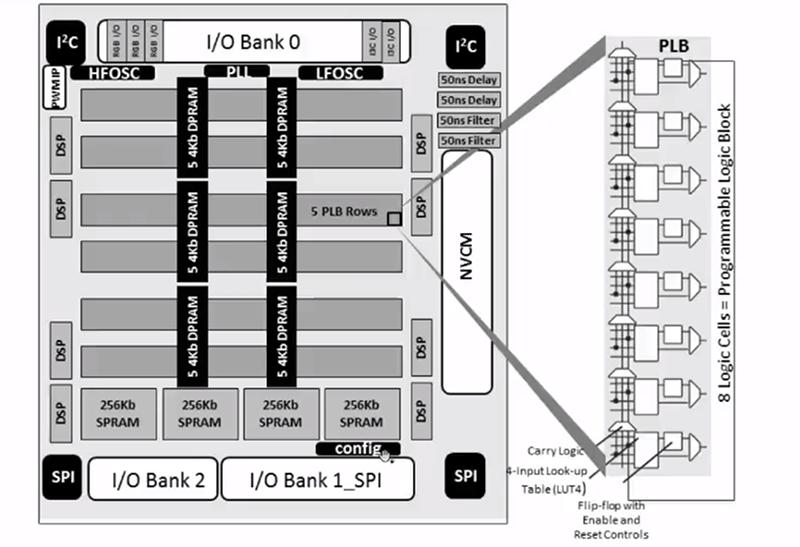

In fact, you might want to watch the video with the datasheets open. The lowest-end UltraPlus device has more logic elements (2,800 vs 1,280) and more RAM (1,104 kbits vs 64 kbit). It also has specialized I2C, SPI, DSP, and PWM hardware onboard. While the HX-1K lacks those extra features, it does allow 98 I/Os maximum compared to the low-end UltraPlus’ 21 I/O. They also have lower maximum propagation delays which means you can usually get them to clock faster than other members of the family.

However, the core fabric is the same: a four-input lookup table (LUT4), a D flip-flop, and some carry logic. More modern FPGAs will often have more inputs to the LUTs to provide denser packing, so be careful comparing one FPGA family’s cell count to another.

Of course, if you are using the iCEstick, you may want to graduate to the more powerful family members and then everything in the videos will apply. They use the UpDuino which is a good upgrade and still very inexpensive. The third video covers the Lattice-specific tools. Be aware that if you want to use the Ultra or UltraPlus devices that Icestorm only supports some of them. If you do use IceStorm, you’ll want to read about the support for newer devices. If you haven’t gotten started with FPGAs yet, why not head over to Hackaday.io and learn more about using the iCE40 in the FPGA bootcamps?

If you buy the iCE40-HX8K Breakout Board (http://www.latticesemi.com/en/Products/DevelopmentBoardsAndKits/iCE40HX8KBreakoutBoard.aspx) which costs not much more than the iCEstick you can synthesize the RISC-V, even with the open toolchain. The RISC-V core code is here https://github.com/cliffordwolf/picorv32

… and you get a ton more IO. It’s a really sweet little board, IMO.

Just checked – that breakout board £37 against £19 for the iCEstick from UK suppliers.

The iCE40 Ultra Plus breakout is also nice. Not as much I/O but you get 128KB SRAM on-chip. Nice for soft-cores. Clifford Wolf – the same person behind the icestorm chain – has synthesized a PicoRV32 on an UltraPlus.

does icestorm work with UltraPlus yet?

yes, the UP5K DOES work with a recent icestorm, thanx to the great effort of David Shah! kudos to him

It would be really neat to have an UltraPlus FGPA with hard RISC-V attached to one of the IO ports instead of just basic i2c or SPI etc which doesn’t save you that much.

That would make for a very powerful development platform… and even lower power.

I’m much more a fan of the MachXO2. It’s a Flash FPGA, so it’s really convenient, it comes in TQFP packages, and it’s cheapish.

I like it too — much better pin IO performance than the ice40 series, because it has support for DDR gearing. I have a bunch of xo2-7000bb’s collecting dust…

Doesn’t have any open source toolchain support though. :(

icestorm toolchain flow is bliss :)

I can build from source a singularity VM with the entire toolchain on my win10 PC at home in about 15 minutes. Rebuilding an SoC design for the hx8k takes about two minutes from changed verilog to programmed chip. Icestudio is even faster — a few seconds, but only to an icestick for now.

For TQFP-144, you can just use an ice40hx4k — it’s actually a rebadged 8k, which the icestorm tools support full use of. (to date, there have been no reports of missing functionality — really looks like lattice just set the ‘4k’ limit in their toolchain software). There’s even a convenient ‘pi hat’ board called the iceZero — part TE0876 from Trenz electronic.

Seems like the ecp5 is just getting some open-source toolchain love now as well, via [nextpnr](https://github.com/YosysHQ/nextpnr). Exciting times!

I wish things like this we’re produced in HTML or even PDF form. Video is:

1) bandwidth hungry (excludes mobile users)

2) fiddly to pause and unpause to consume at your own pace

3) hard to search/seek

4) images suffer from lossy compression.

5) requires headphones to not annoy other passengers on the bus, etc.

6) people generally read and comprehend far faster than they speak, making the time commitment to watch such a video unnecessarily large (especially if only part of it is new to you).

Whereas there is little if anything here that requires video; text with drawings would convey the same content. I expect I am far from alone in having that sinking feeling and moving on every time I find an article like this contains video rather than an actual document.

Are you aware of an open-source i2c block that would work with iCE40 and IceStorm?

https://www.digikey.com/eewiki/pages/viewpage.action?pageId=7569477

I’ve used it and it works. Although you will have to do your own state machine to control it…

OOPS! Here is I2c.

https://www.digikey.com/eewiki/pages/viewpage.action?pageId=10125324

Thanks Al Williams for featuring our videos! This is the first section of a multi-video series on the Lattice iCE40 from UC Irvine (Calit2). We are hoping we can continue to help both the professional and maker communities save time with designs with these videos. Keep up the great work Hackaday!

“Don’t get excited when you see them mention a RISC-V — that isn’t going to fit in your iCEStick”

Yes it does fit in an ICEStick !!

https://github.com/BrunoLevy/learn-fpga

See it at work, at 60 MHz, driving a 128×128 OLed display with a C program compiled with RISCV gcc:

https://twitter.com/BrunoLevy01/status/1270798817575796737