Probably not too many people have heard of Chinese manufacturer GigaDevice who so far has mostly been known as a NOR Flash memory manufacturer. Their GD32 range of MCUs is however STM32-compatible, making them interesting (cheaper) alternatives to sourcing directly from ST. Now GigaDevice has announced during a presentation that they are releasing a range of RISC-V-based MCUs: the GD32V series.

As GigaDevice has not yet updated their English-language website, the information we do have is based on CNX-Software‘s translations from Chinese. The specs for the GD32VF103 series of MCUs are listed by them as follows:

- Core – GD32VF103 RISC-V “Bumblebee Core” @ 108 MHz

- Memory – 8KB to 32KB SRAM

- Storage – 16KB to 128KB flash

- Peripherals – USB OTG and CAN 2.0B

- I/O – 3.3V, 5V tolerant

- Supply Voltage – 2.6 to 3.6V

- Package – QFN36, LQFP48, LQFP64, and LQFP100 packages

Whether they are pin-compatible with the GD32 MCUs is still to be confirmed. If that turns out to be the case, then this might be an interesting drop-in solution for some products. From the specs it seems clear that they are targeting the lower-end ARM-based MCUs such as ST’s Cortex-M3-based STM32F103, which are quite common in a large range of embedded systems.

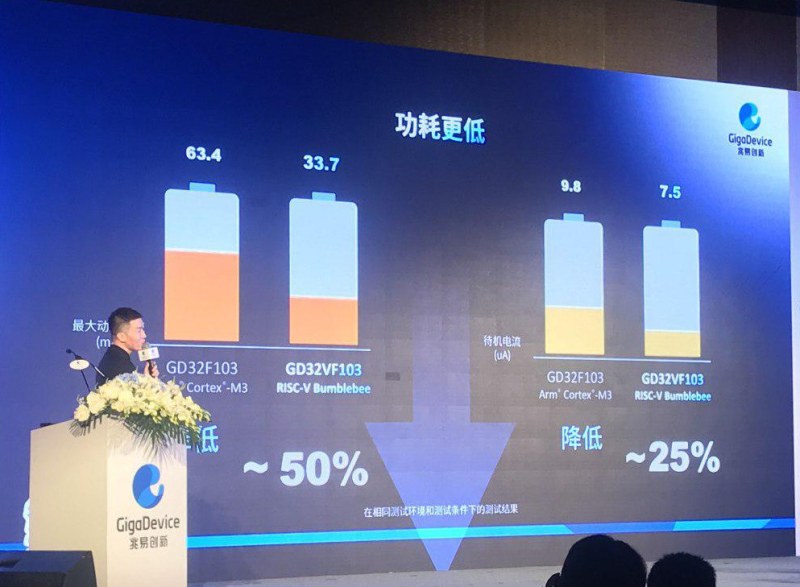

Seeing a performance comparison between both types of MCU would be interesting to see as lower power usage and higher efficiency compared to the ARM cores is being claimed. Both MCUs and development boards are already available for sale at Tmall, with the basic GD32VF103C-START board going for about $11 and the GD32VF103TBU6 MCU (QFN36, 64 kB Flash) for roughly $1.27.

Documentation and SDKs in English seem to be a bit scarce at this point, but hopefully before long we too will be able to use these MCUs without having to take up Chinese language classes.

Thanks to [Flaviu] for the tip!

They have published an SDK with some gcc.exe in there, but without the sources.

That may be ok, as long as they made no changes to the source of GCC. Or they may still offer the source on request.

Common misunderstanding. You still need to supply the source code. Pointing to the original source tree is fine, as long as it is up. But pointing you must.

Would it go down, then would need to supply the source by other means.

https://www.gnu.org/licenses/gpl-3.0.en.html

The license is a bit hard to read. Section 6 is about distributing binaries, first line pretty much says “a binary created from modified or unmodified sources” (rough translation) and then goes into means of which options can be provided for providing the source code.

+1 for you good sir!

From a pragmatic point of view: Do you really want to go to a server in China over the GCC one just because the license say so?

If the main GCC repository went down, there are much bigger problems. :P Beside people who can mess around the GCC is more than smart enough to use google.

The sources are now here:

https://github.com/riscv-mcu

The SDK I am talking about:

http://dl.sipeed.com/LONGAN/Nano/SDK/eclipse_toolchain.rar

Some code might gonna land soon on Github:

https://twitter.com/SipeedIO/status/1166356331768557569

Benchmark are mostly known, very few differences between a Cortex-M4 and a properly designed risc-v RV32IMA. Both are in the same ballpark. So should be better against an aging Cortex-M3.

The (huge) difference is in the interrupt handling. Most risc-v lack NVIC-like hardware and relies on software exception handler. This add a *lot* of overhead on interrupt handling comparing to ARM with NVIC.

The interrupt handler is not part of the RISC-V core. You could add an NVIC clone quite easily. Just set the program counter based on the IRQ line, and put a jump instruction at that location.

NVIC on the Arm does a bit more: programmable interrupt priority. It is also smart enough to chain interrupts and skip the overhead of saving the context. It is part of the core, so even a $0.30 part has it.

Thankfully, they have something very similar to NVIC in this series.

>RISC-V integrates the Enhancement Core-Local Interrupt Controller (ECLIC) for efficient

interrupts processing. ECLIC is designed to provide low-latency, vectored, pre-emptive

interrupts for RISC-V systems. When activated the ECLIC subsumes and replaces the

existing RISC-V local interrupt scheme (CLINT).

Up to 68 maskable peripheral interrupts.

4 bits interrupt priority configuration – 16 priority levels.

Support interrupt pre-emption and tail-chaining.

Wake up system from power saving mode.

—————————————————————— Stuff below are EXTI

Up to 19 independent edge detectors in EXTI.

Three trigger types: rising, falling and both edges.

Software interrupt or event trigger.

Trigger sources configurable.

FYI: English & Chinese datasheet/reference manual:

http://dl.sipeed.com/LONGAN/Nano/DOC/

USB OTG at the low price point is what make this an interesting part.

Dual 12-bit DAC, EXMC (EXternal Memory Controller) – probably in larger chips.

Debugging is with JTAG, so that’ll burn up 4 -5 (TRST) GPIO.

The internal core voltage is 1.2V, so a much newer process than the STM32F part. I/O are 3.3V/5V tolerant.

CNX just made another post explaining the RISC-V extensions:

https://www.cnx-software.com/2019/08/27/risc-v-bases-and-extensions-explained/

Also J-Link supports Longan Nano!

Makes debugging so much easier.

https://wiki.segger.com/SiPeed_Longan_Nano

Maybe it’s time for ARM to open source some of their cortex lines, or at least make them available for free. And not just cores to use in an FPGA.

Sipeed is also producing a cheap board based on GD32V:

https://twitter.com/SipeedIO/status/1164500325119610887

why re-inveting the wheel when you have the common form format of blue pill boards?

If the pin outs are more or less compatible, then existing breakout boards PCB (e.g. blue pill) could be used.

i.e. only important stuff that needs to be the same are power, oscillator, reset, USB lines. The rest are pretty much breaking out the pins to headers without additional components.

Proper USB OTG support would require some minor work.

Oddly some feel with the recent PowerPC reveal, the future of RISC-V may be limited.

https://www.zdnet.com/article/ibms-power-ful-open-source-gift-big-winner-is-china-losers-include-you-know-who/

Some are apparently neglecting the fact that PowerPC, with integrated memory management, deep pipelines, and support for high-speed I/O, is designed strictly for use with multi-user operating systems like Linux or AIX, and is most certainly not going to be competitive on a price level with low-end micro controllers running bare-metal applications powered by coin cells.

It is the “big iron” Power ISA they are opening.

They also have those enhanced, AVR compatible chips.

Sorry, i remembered wrong. They are from logic green. My bad.

Looking into datasheet ( http://dl.sipeed.com/LONGAN/Nano/DOC/GD32VF103_Datasheet_Rev1.0.pdf ) i find out that GD32VF103 is pin-to-pin compatible with STM32F103, at least for LQFP48. That gives good chances that this device quickly gain popularity.

Desolder an stm32 and resolder a gd32v on a bluepill?

Yes, seems that this will work.

I would much prefer a GD-Pill. ie: Blue pill pinout board with GD chip for similar prices from Ebay / Ali / China, etc.

Just ordered 10! Wish me luck! I was going to use a STM anyway, so this might up the nerd factor.