You ever wonder exactly what’s inside that cheap stuff you get from China? Sometimes it is cheap parts you’ve never heard about. Case in point: if you are willing to import, you can score an FPGA board for about $5. The downside? You’ve probably never heard of the GOWIN Semi GW1N — one of the Little Bee FPGAs — that’s onboard.

There is some English documentation which leaves room for interpretation and you’ll have to use their IDE. Then again, it might be a fun puzzle to get one of these working. Looks like Seeed has them available for $4.90.

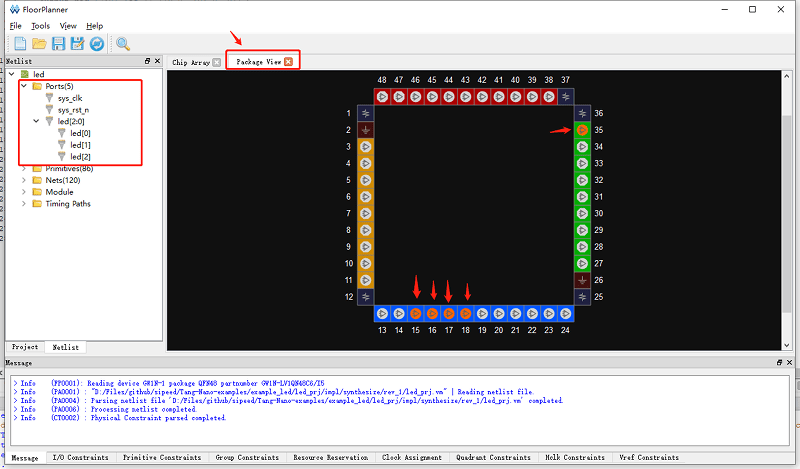

According to the Wiki, the onboard chip is GW1N-LV1QN48C6/I5, equipped with 1152 LUT4 logic resources, 1 PLL and a total of 72Kbit SRAM. The development board brings out all I/O interfaces. There’s also 64 Mbits of PSRAM. The board also has an RGB interface for a display, a 24 MHz clock, and the USB programming/debugging interface.

We didn’t try it, but the development tool looks to be available for Windows or Linux. Browsing through the wiki gives the impression it is usable, although probably simple — which could be an advantage compared to some other tool suites.

Worth a try? The Lattice chips are not that expensive and are well supported by open source tools. Then again, people want to try the very cheap (under a dime) CPU that is in a lot of products. So why not FPGAs, too?

Does anyone know what voltage the GPIO pins are? AFAICT the docs don’t say. I’m desperately looking for one of these boards with 5V TTL I/O.

Based on the data sheet of the FPGA Vmax IO is 3.465V. You will have to add level shifters

Yup; I finally found the board schematic (http://dl.sipeed.com/TANG/Nano/HDK/) and it looks like the FPGA itself runs at 1.2V and the I/O is at 3.3V.

That’s a shame; I’m looking for a cheap and easy 5V CPU-plus-FPGA board which can drive TTL loads to replace my existing PSoC5 board (for this: http://cowlark.com/fluxengine/), which is both too expensive and also has hideously closed source tools. For my application I need to use a single off-the-shelf board, so a custom solution with additional level shifters isn’t an option. I wish 5V parts weren’t so unfashionable these days.

What’s the problem? Normal 3.3V usually guarantees an output high of around 2.9V, which is easily high enough for TTL. Unless you meant 5V CMOS?

Actually, TTL here was shorthand for ‘random collection of poorly-specified stuff’.

The problem is that the technology I’m dealing with, floppy disk drives, don’t actually have a proper specification for the bus signals — it’s all based on ad-hoc good-enough ‘standards’. So I have no idea what technology the drives actually use. Two drives I have datasheets for specify VHI levels of 2.0 and 2.5V, so 3.3V will do fine there. Trouble is, I have no idea how any other drives behave. They’re already flaky enough with regard to bus termination as it is.

So 3.3V might be good enough most of the time but I don’t want to design a product around it. I’d much rather have honest 5V and avoid problems than accidentally design in additional flakiness.

So my last comment above (which I can’t reply to for some reason) is complete rubbish. Turns out the FDD lines are open-collector, which means the master end either drives them to 0V or lets them float. At the slave end they’re pulled to 5V. This means that the output voltage of the master is completely irrelevant; the only important thing is whether the master can sink enough current to pull them to 0V. Apparently, I’m still reading up on this.

Inputs are, of course, easier if there are 5V-tolerant I/O lines although there are some subtleties with pull-up resistors I’m still figuring out.

So, maybe this FPGA will work after all, and apparently I’ve been overly paranoid about this for months. It’s good to know these things…

Just because something labelled “5V TTL” doesn’t mean that it need 5V input. (I am guessing you actually don’t read datasheets)

Read up on your datasheet specifically on the ViL and VIH (inputs for ‘0’ and ‘1’) for things you want to control. Also on VOL and VOH.

VOH (output high) from a 5V TTL is only guaranteed to be 2.4V (min) while typ can be 3.4V because of its output totem pole structure. Guess why they picked 3.3V standard specifically for some TTL compatibility?

5V CMOS parts are the bigger problem.

For CMOS input, the 3.3V is 66% of 5V, so chances are that it would work most of the time. Quick cheat is to lower the 5V to 4.5V (-10%) and that should meet the input specs.

Output would require some voltage translation.

Please don’t be insulting.

As if pointing out technical fact is insulting…

You accused him of willful ignorance (“you dont read datasheets”) which is pretty damn insulting. Sometimes the person you’re responding to actually knows more than you do.

If not insulting, it’s really patronising.

David has been featured here a number of times, and has a reasonably well known blog.

No worries man; other people read public forums & they benefit–that’s the point of a public forum; you’re writing to an individual & to the public…

I’ve never heard of the dude, never read his blog, & otherwise have no knowledge of his data sheet reading habits. I do know his ego is somehow connected to data sheets…(?) The fella’s retort could have been simple, e.g., “I do, in fact, read data sheets.” Instead, he provided deflection…

You seem to know your stuff. Still, snottiness isn’t necessary.

Ah CMOS Vih is actually above 66.666 recurring % of

VccVdd and Vil is below 33.333 recurring %Because back in the bad old days we had fractions and the levels were 1/3 one third and 2/3 two thirds!

Sorry HaD to do it :p

But back on track, a (eh em) year later, it looks like they want an arm and a leg to get a (Free?) licence key so I’m going back to my ISE and Quartus

The comments system limits reply depth, so I’m replying to one of your previous messages.

If you are connecting open-collector I/O lines, at different voltages, you can level convert them with a single N-Channel MOSFET, per line. Connect a pull-up resistor to the 3.3 V I/O pin, so that both the 3.3 V and 5 V I/O pins are pulled high, then connect the gate of the MOSFET to 3.3 V, the drain to the 5V I/O pin, and the source to the 3.3 V I/O pin.

When neither pin is driving low, each pin will be pulled high, to its I/O voltage. The body diode will allow the 5 V I/O pin to pull the 3.3 V I/O pin low, and the MOSFET will turn on, when the 3.3 V I/O pin drives low, also driving the 5V I/O pin low.

You can use any reasonable MOSFET that won’t go over voltage, such as a 2N7000 or BSS123. If you start getting into the MHz range, you will need to source a part that allows a faster switching time, and use stronger pull-up resistors.

“Open Collector” is from the BJT era so it works well with BJT’s.

So just have a uC drive the base of the transistor through a resistor (1k-4k7) and leave the collector “open” the collector line is then connected through a pull up resistor to whatever Voltage the Vcc is at the other end.

Problem with the PSoC5 board is that while the tools are closed soured, the chip isn’t. All the register’s that route the luts and other blocks are all memory mapped so you just need to set the bits.

The problem is there isn’t a tool that can easily do this. They basically gave up after the first version of the Creator and Interion just made stock components and killed off the line. It might of been better if they just used the same idea from the PSoC1 line and just have the user connect the routing and settings in a picture rather than the hodgepodge way they did it in Creator. Still I give them props for trying something different.

Do what I did and use GreenPAK. Granted the chips are SUPER small but they are cheap, can cross voltage domain AND can be reprogramed live with i2c. All of them have more logic thank even an ATF2500. Renesas seems to be the only manufacture still making MCU that run at 5V and most of their stuff is tolerant. They even came out with a low lut fpga (1100, I think they are using the QuickLogic IP for it) but like most FPGA’s now a days you need a 1.2v regulator and only handles io to 3.3v.

Go with GreenPAK and one of their dip development boards for like 10 bucks. Its fast enough to decode MFM data from a hard drive at 6mbps to SPI.

Yep correct, but the Gowin FPGAs have switchable PCI clamping diodes. So if you can get away with 5V tolerant IOs, then just add a series resistor to limit the current over the clamping diode to a tolerable level. Of course prior configuration of the logic the pins run without these clamping diodes, you have to account for this. Other than that a fet bus switch (Fairchild semi for example) makes also a nice bidirectional level shifter without the need for mucking around with a direction pin.

Nope, it’s 1.2V for LV core, and 1.8V/2.5V/3.3V for UV core.

https://alcom.be/wp-content/uploads/2018/09/GOWIN_100918_DS100-1.2E_GW1N-series-of-FPGA-Products-Data-Sheet-1.pdf

“VCCO of LV devices can be set as 1.2 V, 1.5 V, 1.8 V, 2.5 V, or 3.3 V

according to requirements.”

– It smells like up duino in here…

– Hey what’s upduino?

BTW how many LUTs do i need for basic RISC-V core?

It appears to vary by architecture and how many non-LUT resources the FPGA has available — https://github.com/SpinalHDL/VexRiscv has a list. But it looks like it’s at least plausible.

It should be enough for some configurations of PicoRV32: https://github.com/cliffordwolf/picorv32

Though you wouldn’t much room to fit much else on there. Maybe a simple UART and a driver for the QSPI PSRAM if you’re lucky. Don’t know how much block ram you’d have left over. But I suppose it’d get you enough to run it as a cheap microcontroller class device.

You should be able to fit a couple of SERV cores https://github.com/olofk/serv on that device. Haven’t had time to try it yet though

Note minimum $10 shipping to Australia by Seeed.

If you switch the GOWIN website to English, all technical documents have a version number that ends in “E”. To download them, you have to register, but the form does not ask for crap like the company name or the number of devices sold in the first year.

https://github.com/sipeed/Tang-Nano-Doc

It is available via aliexpress !, it costs like 9 bucks:

https://de.aliexpress.com/item/4000301629311.html?spm=a2g0o.productlist.0.0.701015a9Ajs8af&algo_pvid=02c25474-84ff-42ab-ba1e-7a4ade7ef3bd&algo_expid=02c25474-84ff-42ab-ba1e-7a4ade7ef3bd-8&btsid=6b9536ce-346b-423d-9e29-e480e8158697&ws_ab_test=searchweb0_0,searchweb201602_1,searchweb201603_55

Would be great to have opensource toolchain for this… Eg. yosys, apio or icestudio.

https://hackaday.com/2016/02/23/icestudio-an-open-source-graphical-fgpa-tool/

Also it would be great if JLCPCB had this chip on stock for their PCBA service (along with other cool FPGA chips like ICE40 and ECP5)

If it’s the same tools that Lichee Tang it works relatively well. http://www.fabienm.eu/flf/deballage-du-kit-de-developpement-lichee-tang-muni-dun-fpga-chinois-anlogic/

My mistake it’s gowin fpga, then it should be the same tools as LittleBee : http://www.fabienm.eu/flf/le-point-gowin/.

There is lot of confusion about board names. There’s “Lichee/Sipeed Tang Nano” with Gowin GW1N-1 FPGA (1K LUT) and “Lichee/Sipeed Tang Premier (primer?)” with Anlogic EG4S20 FPGA (20K LUT and built-in 12-bit 1MSPS ADC).

Some software can be downloaded at http://dl.sipeed.com/

Gowin Linux IDE takes 1,2GB and i didn’t managed to get it working on ArchLinux yet

Anlogic Linux IDE takes 120MB and worked first try on ArchLinux after setting chmod +x and typing ./td -gui

Anyway i would still prefer to have real FOSS toolchain before investing to development of product using such chip.

So while anlogic is bit more expensive, it seems to offer much more. But for the price of $20 shipped, you might be able to get FPGA board with IC made by some bigger brand (Can as well get CYCLONE IV EP4CE board for $20 on Aliexpress, but that does not have opensource toolchain either, so i will leave this up to you).

BTW I bought a Spartan 6 + SDRAM board on aliexpress for $20 shipped.

These have 5 volt tolerant IO as well:

http://www.latticesemi.com/en/Products/DevelopmentBoardsAndKits/ispMACH4256ZEBreakoutBoard

Count me out, when it comes to fpga’s and CPLD’s I’ll take more mainstream and documented devices like Altera Cyclones or older Xilinx chips.

Don’t care if the software is closed source, it’s free and well documented. Sure it has a learning curve but then again FPGA’s aren’t for everyone.

> FPGA’s aren’t for everyone.

ROFL. Wait a year or two old man. Trust me. FPGAs will be the new Arduinos in no time. With FOSS drag and drop tools like icestudio, your grandkids will program FPGAs as soon as they will understand how LEGO bricks fit together.

BTW what do you think about Lattice? Is that mainstream enough for you? They seem to have the best of two worlds (proprietary and opensource).

I’ve used Lattice parts for over a couple decades, I started with PAL’s and GAL’s. It’s too bad they don’t make them anymore. Nice “glue logic” solutions for many projects where it was overkill to use a FPGA.

Sadly Lattice today doesn’t really do PLD’s anymore and what they do have is hobbyist unfriendly as hell in terms of packaging. So I use the PLD’s from Microchip or use some of the older offerings from Altera like the Max 3000 series.

Gnarly grey boards are fine low cost entry ways into the world of FPGA’s as are the older Altera cyclone boards you can find on Ebay or Alibaba.

IceStudio shows a lot of potential even being a .5 rev. at this time. it’s not at the level of LEGO’s where you can mindlessly put something together nor should it be. That’s a good way to shoot yourself in the foot on anything more complex than turning LED’s on and off.

BTW what is the cost of moving from one FPGA brand to another if you decide to change it later down the development process? Are there any changes needed to be done in your VHDL/Verilog code at all? I understand that you have to redo the pin assignments to fit your logic into layout of different chip and rerun the “place & route” software to reflect different chip constraints. But that should be about it… Did i understood that correctly?

It depends on how specialized the design is. I have simple designs that would work on any family, and also very high performance designs that only could exist on one vendor’s chips. DSPs, for instance, are wildly different between chips.

If you’re just using HDL, it’s fine, but for any high performance design I have, they’re *loaded* with vendor specific primitives.

As Pat says, it depends on how much of the device specific features you are using in your HDL.

If you are pushing the boundarys of your timing envelope then a different part may make or break your project. This is also very true between device families from the same manufacturer.

And you’ll have to re-lay out your PCB as some pines are dedicated to certain functions, and devices come in different non standard packages with differing amounts of I/O available to use.

Usually its best to pick a part, that allows you to go larger/smaller in LUT/Cells etc whilst staying in the same foot print. This is something we’ve just been bitten by as we had already maxed out the FPGA size in the foot print we were using, and are now having to re-lay the PCB for a new foot print.

I would usually avoid changing brands during an engineering effort, unless you really had the business/application case behind it.

Software guys need to get it in their heads that HDLs are not procedural programming languages as it describe hardware which runs in parallel.

What? Do you think there are guys that do HDL programming without understanding this? And how it’s related to my question? I’ve asked about transition between FPGA brands, not about transition from sequential logic to combinational logic.

I like this Gnarly Grey FPGA-Boards:

http://www.gnarlygrey.com/?i=1

They are quite cheap and there is also an open source tool chaine.

Is the USB port really meant for FPGA programing? From some photos on the internet it got the impression that you have to use externall programmer to program the FPGA, which can then use the USB port once it is programmed.

The more expensive “lichee tang premier” sometimes comes preprogrammed with RISC-V core, which then effectively makes it a MCU programmable in C language using USB just like arduino. But i am not sure if the USB interface can be really used to reprogram the FPGA to be something other than RISC-V MCU, that might need an additional programmer. (which is still not very expensive).

Am i missing something? Is there way to program these FPGAs purely over USB without any additional hw? OTOH wouldn’t it mean that USB is only for programming and cannot be used by FPGA for other purposes?

I am really confused. Is there somebody who has actual experience with theese boards?

Looking around it seems very clear that the USB port is for power and download only.

Unforunately last I checked about 1 year ago you’re better off using a Phy.

For example tinyFPGA has dualboot over spi and USB directly to gpios.

Shameless plug of my Openalt presentation. Minute 17 https://youtu.be/S-Qxf9ZS3B8

Don’t worry. I’ve already saw your talk before this hackaday article came online. Unfortunately i’ve missed the OpenAlt this year. However i am glad that you are sharing the message in Czech republic. FPGA and opensource ecosystem around them needs much more attention, because it’s so cool!

Nice, my go to PLD are those dirty cheap EPM240 boards you see on eBay for £5-£10.

This is a nicer form factor and looks better put together (got to inspect those boards from eBay). But 34 I/O is mostly enough, the CPLDs have about 100 brought out.

Still nicer to have over 1000 proper LUT4.

I’ll have to see the IDE before that decision is set, the flow on PLDs is so bad I find myself using a lattice just so I can use icestorm.

Interesting and worth a look and maybe for yet another weird power project, thanks for posting :-)

Cheers

Pls guys can you help clear the air on FPGA and PLC which of them is widely and commonly used by industries?. Thanks

A PLC and an FPGA are two very different types of devices. And different industries use them differently.

PLC stands for Programmable Logic Control, this is usually a box that can most normally be mounted to a DIN rail, and it typically has all sorts of IO capability, but most normally oriented towards industrial control of automated manufacturing setups and jigs. Ie, it can switch anything from low voltage DC to high voltage AC by the help of relays. PLCs are very common in heavy industry.

An FPGA is “similar”, but just a chip. It doesn’t come with screw terminals, nor relays. Isn’t easily programmed via a network interface from the other side of the world, and it doesn’t just “take” 5-24 volt power and “just work.” FPGAs also don’t just mount to a DIN rail, or have premade control software for them. Also, FPGAs are extremely sensitive to ESD, unlike a PLC that at times are designed to survive having mains voltages applied to their low voltage DC IOs…

An FPGA is similar to a microcontroller, or a PCB with hundreds/thousands of logic chips on it, but where the connections between these chips is defined via software, its a bit like a breadboard.

These two kinds of devices are not interchangeable. The PLC is a finished product, the FPGA is a component that is useless if its alone.

The FPGA is though common within products in industrial environments, like being the chip that runs PLCs.

An FPGA is simply a semi cost effective method of having a “custom” chip, without the expense of making an actual custom chip. (Making a custom chip (aka ASIC) is usually only cost effective if one makes tens of thousands of chips, or have a very special application. (Usually analog/RF/high-performance-DSP in the later case.))

For those interested, I’m currently working on support for Gowin FPGA’s in the open source tools. I expect a release somewhere December. Meanwhile, I post updates on my twitter @pepijndevos

This is super interesting! Shoot us a tip (tips@hackaday.com) when you’re ready.

Wow! Following you on Twitter. Agree, this is VERY INTERESTING!

Oh by the way, you can get nice Lattice FPGAs of the iCE5LP1/2/4K variety quite cheaply also, typically under 4e apiece. They do seem to need a few supply rails however.

I really wish I could get a board in this price range and # of gates, etc. but with more pins exposed. 64 pins would be my requirement, but given that the FPGAs on these boards have plenty, it’s a bummer they don’t expose more.

Amazing work! How far did you get? Is it possible to use open source tools with Gowin’s FPGAs?

> Is it possible to use open source tools with Gowin’s FPGAs?

Yes it is ! You can use openFPGALoader to configure the FPGA :

https://github.com/trabucayre/openFPGALoader

And Apicula project to synthesize, place&route then bitstream it :

https://github.com/pepijndevos/apicula

French explanation for apicula here :

https://linuxfr.org/news/apicula-lancement-de-la-liberation-du-fpga-gowin-gw1n

Amazing!