One of the problems with designing things on a chip is finding a good way to talk to the outside world. You may not design chips yourself, but you care because you want to connect your circuits — including other chips — to the chips in question. While I2C and SPI are common solutions, today’s circuits are looking for more bandwidth and higher speeds, and that’s where Interlaken comes in. [Comcores] has an interesting post on the technology that blends the best of SPI 4.2 and XAUI.

The interface is serial, as you might expect. It can provide both high-bandwidth and low-latency multi-channel communications. Interlaken was developed by Cisco and Cortina Systems in 2006 and has since been adopted by other industry-leading companies. Its latest generation supports speeds as high as 1.2 Tbps.

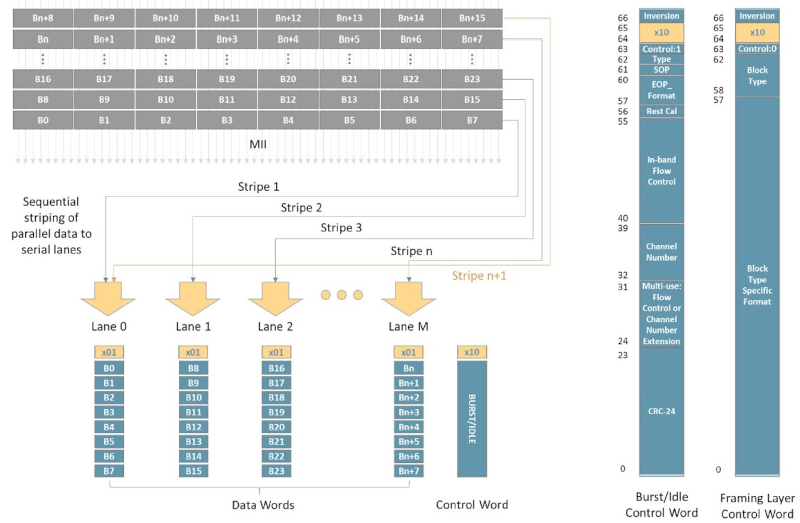

Interlaken can support up to 65,535 data streams and features error correction. The interface also handles retransmissions, so the users don’t have to. Interlaken uses a meta-frame concept. For each lane, a set of words associated with the meta-frame are sent along with the payload of control and data words. These include alignment information, clock compensation, status information, and error-checking data.

Unless you develop chips or build FPGAs, you probably won’t worry too much about the internal details, at least not yet. But the time may be near when the next cool device the delivery guy leaves on your porch expects to use Interlaken for communicating with the outside world.

Meanwhile, there’s I3C (not I2C, mind you). Then again, for the kinds of things we do, there’s nothing wrong with good old SPI.

Its a small typo

I assumed it was some kind of ‘stop cock’, possibly connected to a flange via a ‘barrel nipple’.

It’s perfect for the somewhat obscure field of teledildonics.

hehe

Looked into Interlaken a long time ago but then came to the conclusion that PCIe was a better choice for what our customer wanted to do.

+1 already on board, scales well, has legacy speeds.

Don’t re-invent the wheel. Even if you want to tweak the lanes and call it DMI or something.

TCP/IP over USART or SPI is a good choice for connecting couple microcontrollers together.

Inserting requisite [url=”https://xkcd.com/927/]”Standards” xkcd comic[/url] here.

Inserting requisite “Standards” xkcd here: https://xkcd.com/927/

Fixed. Thanks.

It says “Nine thoughts…” but only shows four. Something to do with the earlier “clock-up”?