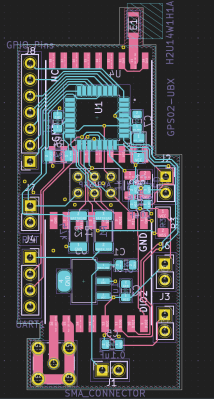

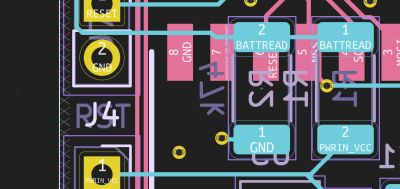

Welcome to the Design Review Central! [VE3SVF] sends us their board, and it’s a HAB (High Altitude Balloon) tracker board. It’s got the venerable ATMega28P on it, a LoRa modem and a GPS module, and it can be powered from a LiIon battery. Stick this board with its battery onto a high-altitude balloon, have it wake up and transmit your coordinates every once in a while, and eventually you’ll find it in a field – if you’re lucky. Oherwise, it will get stuck hanging on a tree branch, and you will have to use a quadcopter to try and get it down, and then, in all likelihood, a second quadcopter so that you can free the first one. Or go get a long ladder.

The ATMega328P is tried and true, and while it’s been rising in price, it’s still available – with even an updated version that sports a few more peripherals; most importantly, you’re sure to find a 328P in your drawer, if not multiple. Apart from that, the board uses two modules from a Chinese manufacturer, G-Nice, for both GPS and Lora. Both of these modules are cheap, making this tracker all that more accessible; I could easily see this project being sold as a “build your own beacon” kit!

Let’s make it maybe a little nicer, maybe a little cheaper, and maybe decrease the power consumption a tad along the way. We’ll use some of the old tricks, a few new ones, and talk about project-specific aspects that might be easy to miss.

The Low Hanging Fruit

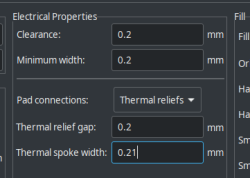

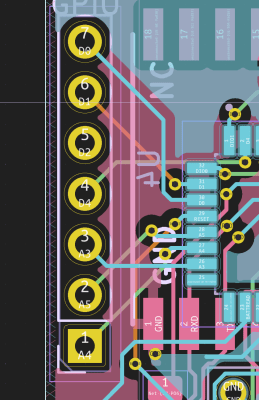

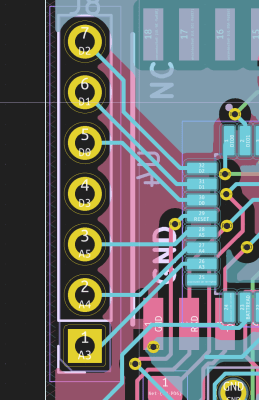

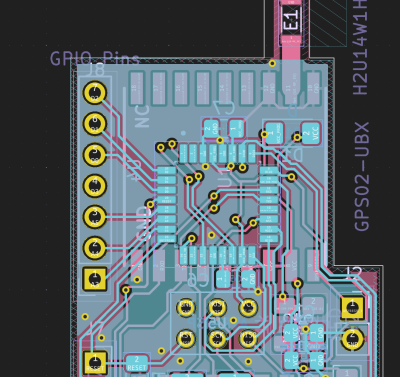

This board has four layers, which is nice because you get more ground and more routing space for a tiny price increase these days. This board doesn’t add fills on inner layers, but that is an easy fix – just select one of the GND power planes and tick the In1/In2.Cu boxes in their settings. Another thing to tweak in zone settings is zone clearance and minimum thickness – default KiCad clearances are way too conservative, setting them to something like 0.2 mm / 0.2 mm is a good idea. That improves ground connectivity, and also lets us get rid of ground tracks that would otherwise be necessary to bring ground to different connectors.

The inner layers have ground, and ground on all layers can reach further, too. That said, the inner layers benefit from being completely free – that’s when you get the best return current flow. Remember, each track, whether signal or power, needs its ground return path, and if you don’t provide a direct clean one, electricity will find a way. That, in turn, results in noise, both received and emitted, as well as possible instabilities.

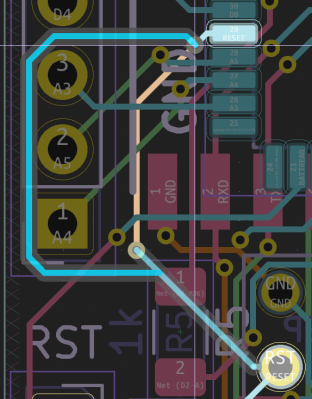

In particular, the ISP flashing header had a lot of low-hanging fruit; tracks that were pulled on inner layers but could as well go on top/bottom layers. Many tracks could be snaked between GPS and LoRa module pads, too – the gaps are wide enough, that even a 0.2 mm track feels comfortable in there, and you could probably pull two if you dropped down to 0.15 mm, which is still safe with most fabs.

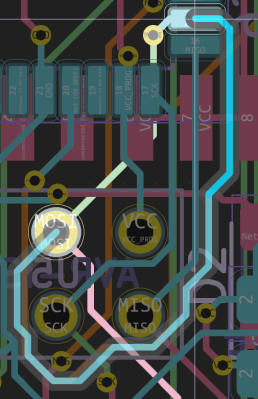

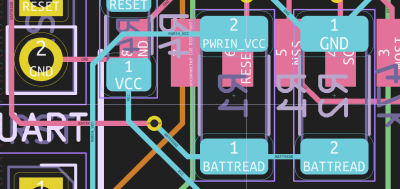

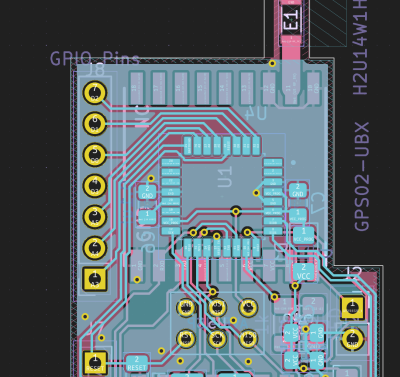

And, after a dozen minutes of work, the inner layers are free. A surprising amount of space could be found – for instance, the three DIO tracks nicely went along the right edge of the board. More importantly, capacitors were moved closer to where they work best. In particular, the AREF capacitor is two vias and one long inner track apart, which won’t make for good analog decoupling. That did require moving the ATMega a bit upwards, but a judicious application of Del and Shift+Del on tracks, as well as some track dragging, made that move go quickly.

I could talk about component size choices, but they’re not meaningfully interfering with routing on the board – even the opposite, having one of the diodes be 1206 helps me avoid some vias. On the other hand, rotating the battery divider resistors and power regulators 180 degrees resulted in some good routing space freed up. And, looking at the board, the ATMega328P routing could perhaps use being rotated one turn clockwise, too. That’d make SPI routing cleaner, power tracks and analog pins shorter, and let us put capacitors at the sides, at the low low cost of having GPIO pins snake around a bit. However, here, the benefits aren’t necessarily as clear-cut as in previous articles; instead, it’s a time vs niceness tradeoff.

The Chip Gets Rotated, But Not Necessarily

Here, a conundrum. We could spend maybe a dozen more minutes and rotate the chip, or leave it be? Is the board going to be slightly nicer? Yes. Is this necessary? No. If you want to just order the board and go, it’s completely fair for you to press order and leave improvements of this grade for rev2. On the other hand, if the itch to improve your board is bad enough that the time investment doesn’t scare you out of it, give in and see yourself become better at PCB design. Worked for me.

There are hidden problems for such small redesigns, though. Remember, a redesign might have you reinstate a problem that you’ve successfully avoided with the original iteration, or, it can quickly become infeasible. I’ve had it happen, where a redesign that intended to add features and reduce complexity has become counter-productive midway through, so, I’ve had to stop myself from continuing and just order the board already. You’ll learn to keep track of these, but it does take keeping it in mind. Keep your Ctrl+Z’s ready, keep a copy of the files, or a Git commit, if you are doing something fundamental, and be ready to get a lesson in letting go.

I ended up rotating the chip, and the board did indeed become a bit nicer, but in ways that don’t solve any pressing problems. By the way, have you noticed something this board has done really well from the start? That’s component placement. The ways the LoRa module, GPS module, ATMega328P and the headers are positioned, I wouldn’t change anything about them. Maybe move the pin headers onto a 2.5 4mm grid so that you could expand this board with a perfboard if needed, but that one isn’t a must – this is a low weight board, after all, the headers are more for debugging than anything else.

Last Thoughts: Inner Layers And Antenna Choice

If you have internal layers, use them for ground or power fills, so that power and return currents can flow unrestricted. This is going to reduce both radiated and received emissions, as well as make power rails smoother, which feels mighty helpful considering this design has two radios on it and the GPS radio has a passive antenna.

Also, some fabs don’t want empty inner layers. Last year, JLCPCB started refusing multi-layer boards with inner or outer layers less than 30% full, in what’s presumably an attempt to decrease the etching process costs, causing some people to redesign perfectly working PCBs with little notice. Combine this with a recent documentation overhaul that just so happened to turn some previously free options into paid ones, and if I were to guess, they are no longer able to keep running at a loss as much as they did, so, the age of golden offers at JLCPCB might soon to be over.

Our improvements ended up providing more than enough copper on top and bottom layers, that you could possibly switch this board to two-layer; again, cheaper ordering, possibly quicker manufacturing time, possibly cheaper PCBA. Isn’t a requirement, but it is nice when you can do it. If you are to keep the two extra layers, remember that on-board antennas need keepouts at least for a wide patch under them, if not for a good amount of space around them, and the keepout has to be on all layers. No tracks, no fills, no copper, do not pass go, do not collect 200.

Our improvements ended up providing more than enough copper on top and bottom layers, that you could possibly switch this board to two-layer; again, cheaper ordering, possibly quicker manufacturing time, possibly cheaper PCBA. Isn’t a requirement, but it is nice when you can do it. If you are to keep the two extra layers, remember that on-board antennas need keepouts at least for a wide patch under them, if not for a good amount of space around them, and the keepout has to be on all layers. No tracks, no fills, no copper, do not pass go, do not collect 200.

Thicker tracks for power paths are good whenever you can afford them – and this board has plenty of space! I personally usually add them in last, and it’s not a problem here, but it’s most certainly a smarter decision to draw them thick first so that you don’t have to do a re-layout later.

It also does feel like you could consider an active antenna here. For a high-altitude balloon, sure, you’re way way more likely to get a fix and you’ve got a whole lot more time to do it, but I would guess improving your chances is worthwhile. Plus, I don’t know much about G-Nice’s modules, still yet to try out the one I purchased last year – it might be that this module is perfectly okay, but it concerns me these are meant to be footprint-compatible drop-in replacements for well-established company modules, with this specific module borrowing an U-Blox footprint, and as such, I don’t know how much to expect. An active antenna adds a fair of weight and size footprint, and it might be that everyone’s flying with passive antennas no worries, so I might be completely out of my zone here. Whichever is the case, I would appreciate input!

As usual, if you would like a design review for your board, submit a tip to us with [design review] in the title, linking to your board files. KiCad design files strongly preferred, both repository-stored files (GitHub/GitLab/etc) and shady Google Drive/Dropbox/etc .zip links are accepted.

“Also, some fabs don’t want empty inner layers. Last year, JLCPCB started refusing boards with inner or outer layers more than 30% full…”

Should “more” be “less”? When you say “empty”, do you mean void of copper (I’m assuming) or void of tracks? I think a slight rewording here would help readers understand.

Not void of copper, FILLED as continuously as possible.

Do you have a reference for this JLCPCB restriction? I couldn’t find any and I had a 4-layer run less than a year ago which had internal ground planes. It’s common practice and actually saves them money. Maybe it was LESS than 30% full. They do say they will add pours where necessary, so that would make sense.

yep, that was a mis-statement, my bad! jlc complained about too little copper, to be clear, so indeed LESS than 30% full

I ran into this issue on the last board I ordered (I also wasn’t aware of this restriction). I haven’t been able to find any official notes on JLC’s website about this requirement, but here’s what JLC support had to say over email (as of April 2024)…

“If the copper areas are less than 30% of the board in outer copper layer, the space between trace and trace should be at least 0.15mm to avoid short circuit. The space in your file is not enough.”

I later got even more clarification… “If the copper areas on ttop and bottom copper layer is more than 30$, this problem will be solved.”

The tight spacing was on some differential traces that I didn’t want to tweak. I ended up canceling my order and adding some copper pour to the top plane. When I re-ordered with the new gerbers I didn’t run into any issues.

Oh, hm. That’s interesting. So if you have too much “no copper” space on your board, then the inter-trace spacing needs to increase, presumably because jlcpcb can’t guarantee that the etch will get as close to your artwork in the limited etch time for the panel. I think that makes sense? So it’s a combination of “too much copper to etch” *and* “traces close together” that makes the difference between your case (which JLC had issues with) and mine (which they didn’t).

Agreed, I tripped up on this as well. Usually it’s too much “lack of copper” that the fab house doesn’t like, since it starts with “all the copper” and has to etch to make “no copper”. I’m assuming that’s what they are complaining about.

Although I just submitted a sizable board that, for artistic reasons, consisted of fine traces over the entire board surface but much less than 30% of the total area occupied by copper, and I didn’t get any complaints from JLCPCB. So I don’t know exactly what is meant. (https://github.com/cscott/TouchpadSpacerFW16 with a better picture at https://community.frame.work/t/touchpad-with-2-buttons-instead-of-clickpad/36343/18 )

An active antenna is a waste of space, mass, and power on a balloon, unless your receiver has spectacularly poor sensitivity. Those are for dealing with long cable runs and signals weakened by obstructions, neither of which applies when the antenna is kilometers from the nearest RF-opaque object and millimeters from the receiver.

that makes sense, exactly the kind of insight I was wondering about when writing that paragraph!

This read leaves me interested…is this by chance an open source project – or at least planned to be?

0.15 mm = 6 mil traces.

I like it when dimensions are given in both systems, especially when trace widths are often specified in mils.

what’s a mil?

An Imperial measurement unit.

A “Mil” is 1/1000th of an inch. Converted to metric its 25.4 micrometers or 0.0254 milimeter.

Lots of Electronics Design Automation (EDA) programs default to using “Mil” as unit of measurement.

It’s funny because dividing by a thousand is a very metric thing to do.

And deeply annoying because I say “mil” when I mean “millimetres”, and am pretty sure it’s widespread in the metric-only world too. At least that’s only an issue for speech, not for anything written down.

Which software is used for the board design?