[Sebastian Lederer] has created Tridora: an unusual stack-based CPU core intended for FPGA deployment, co-developed with its own Pascal compiler. The 32-bit word machine is unusual in that it has not one but three stacks, 16-bit instruction words, and a limited ISA, more like those of the 8-bit world. No multiply or divide instructions will be found in this CPU.

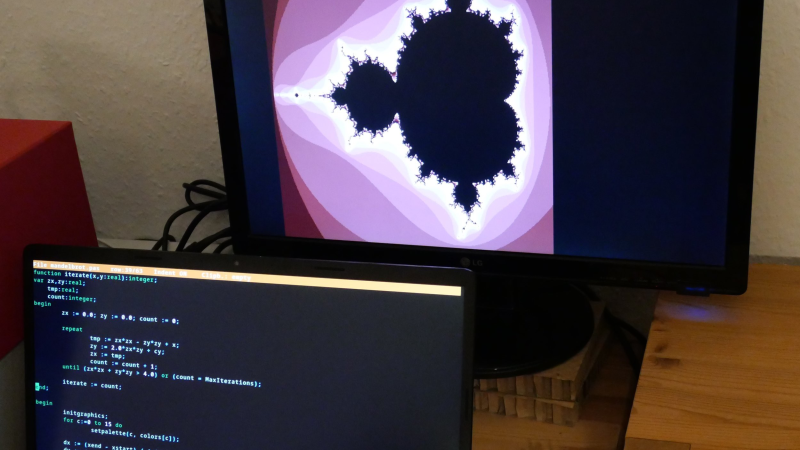

The design consists of about 500 lines of Verilog targeting the Digilent Arty-A7 FPGA board, which is based around the Xilinx Artix-7 FPGA line. [Sebastian] plans to support the Nexys A7 board, which boasts a larger FPGA array but has less RAM onboard. The CPU clocks in at 83 MHz with four clock cycles per instruction, so over 20 MIPS, which is not so shabby for a homebrew design. Wrapped around that core are a few simple peripherals, such as the all-important UART, an SD card controller and a VGA display driver. On the software side, the Pascal implementation is created from scratch with quite a few restrictions, but it can compile itself, so that’s a milestone achieved. [Sebastian] also says there is a rudimentary operating system, but at the moment, it’s a little more than a loader that’s bundled with the program image.

The Tridora Gitlab project hosts the Verilog source, an emulator (written in Golang, not Pascal) and a suite of example applications. We see quite a few custom CPUs, often using older or less popular programming languages. Here’s an FPGA-based Forth machine to get you started. Implementing programming languages from scratch is also a surprisingly common hack. Check out this from-scratch compiler for the Pretty Laughable Programming language.

It reminds me of Western Digital’s Pascal Microengine from 45 years ago.

Aha, a P-code machine. Thanks :-)

https://alchetron.com/Pascal-MicroEngine

http://www.staroceans.org.s3-website-us-east-1.amazonaws.com/wiki/A/Pascal_MicroEngine

I was working at WD in Costa Mesa when they were winding down the PM production. Given what a mess it was then I’m still astounded they’ve survived until now.

The UCSD p-Machine was certainly one of the inspirations for the Tridora-CPU. The design and the instruction set is more like the J1 CPU (or the N4016), as others have mentioned.

Based on the J1 FORTH processor verilog but you have to dig fairly deep to see that!

I love the J1’s design. It was a lot of fun to read through the Verilog for it!

I still want to turn my wild notebook ideas into a working architecture (that nobody will actually use). I have some notes sketched out to do something like the AVR instruction set but with some addressing extensions (segment registers) and 16-bit operations. (32-bit operations would be ideal, but then it starts to look like MIPS with unnecessary complexity on top)

Can you elaborate a bit?

No.

Still impersonating Dave to post dumb stuff? Why bother?

…and the source IP came from a Tor exit node, so unless the Real Dave Jones®© is posting dumb stuff via the Tor network, I guess we’ll never know.

Because the compilers are easy to write. Doing a single pass Pascal compiler for a stack machine is basically what the text book teaches. And Pascal isn’t as ugly looking as C, but that’s more of a subjective opinion than an objective argument.

(I say this as someone who has worked professionally doing either C or C++ for 25 years)

Running a bit more with the Pascal MicroEngine subtopic. The Raannd (a Scottish company, though it looks like it ought to be Dutch or South African) SP1 was a Pascal MicroEngine computer reviewed by Personal Computer World in December 1980 (page 52).

https://www.worldradiohistory.com/UK/Personal-Computer-World/80s/PCW-1980-12-S-OCR.pdf

PCW had its own set of Pascal Benchmarks, which are handily covered in the very next article. The performance for the Raannd SP1 is (the values are the number of seconds taken to run the bench tests, so higher = worse):

Magnifier: 0.85, ForLoop: 9.52, WhileLoop: 9.29, RepeatLoop: 9.09, LiteralAssign: 11.02, MemoryAccess: 11.45, Vector: 26.4, EqualIf: 15.96, Unequalif: 15.78, RealAlgebra: 6.79, RealArithmetic: 8.75, NoParameter: 4.55, Value: 4.96, Reference: 4.98, Maths: 7.00.

So, a lot of benchmarks!

In their Pascal Benchmarks article they also list the performance for a Heathkit H-11A, based on an LSI 11/2 running UCSD (+the EIS chip). Given that the LSI 11/2 will be running a p-code interpreter (but a very similar microarchitecture), we find that the Pascal MicroEngine is about 5x faster.

I have read that another machine that was frequently used at universities to run the UCSD p-System was the Terak 8510/a. It was also based on the LSI-11 which in turn was based on the MCP-1600 from WD, which was also the basis for the Pascal-MicroEngine.

So I wonder what might have happened if someone put the Pascal-MicroEngine variant of the MCP-1600 into the Terak. A desktop computer with a fast UCSD-p-System and a bitmapped display should have been pretty neat at a time when the IBM PC did not exist yet.