This week, IBM revealed their POWER10 CPU, which may not seem too exciting since it’s primarily aimed at big iron like mainframes and servers. The real news for most is that it is the first processor to be released that is based on the open Power ISA specification v3.1. This new version of the Power ISA adds a number of new instructions as well as the notion of optionality. It updates the v3.0 specification that was released in 2015, right after the founding of the OpenPOWER Foundation.

Currently, a number of open source designs for the Power ISA exists, including MicroWatt (Power v3.0, VHDL) and the similar ChiselWatt (written in Scala-based Chisel). In June of this year, IBM also released the VHDL code for the IBM A2 processor on Github. This is a multi-core capable, 4-way multithreaded 64-bit design, with silicon-implementations running at up to 2.3 GHz and using the Power ISA v2.06 specification.

The ISA specifications and other relevant technical documentation can be obtained from the OpenPOWER website, such as for example the Power ISA v3.0B specification from 2017. The website also lists the current cores and communities around the Power ISA.

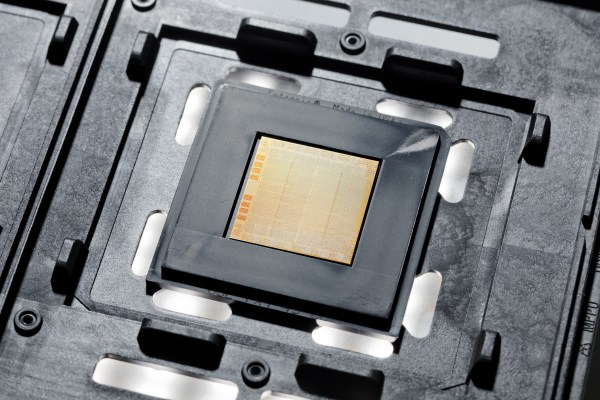

(Main image: POWER10 CPU, credit IBM)