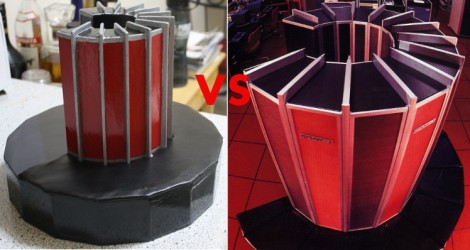

[Chris Fenton] spent a year and a half constructing a 1/10th scale Cray-1 reproduction. The famous supercomputer was meticulously modelled in a field programmable gate array for a “nearly cycle-accurate” reproduction. [Chris’] hardware of choice for the project is a Xilinx Spartan-3E 1600 development board, using 75-80% of the available resources. The finished product runs at 33 MHz and is missing a few functions but it sounds like they don’t affect code execution. We like that he didn’t stop with the processor implementation, but also took the time to produce a case for the development board that looks just like the original.

Unlike the Atari 2600 FPGA project, we’re not quite sure what we’d use this for. But that doesn’t diminish the excellence of his work.

Awww, aren’t you the cutest little supercomputer, aren’t you? Yes you are!

Why 33Mhz rather than the original 80Mhz? Is this a limitation of the FPGA used? Granted, even the original speed is no longer impressive by today’s standards, but given that he went to the trouble of making the detailed case, I’m surprised he didn’t go for the original speed.

can it do the amazing power of the 136MFLOPS that the original can do?

its unsurpassed my today’s *cough*pocket*cough* COMPUTERS!

i know the cray XT5 can do over 1 PFLOPS

Great looking project. I’m not sure you will find a copy of the OS but lets hope I’m wrong.

Probably cost Jonathan, the fpga’s get spendy really fast above those levels.

Awesome project.

I like it! That’s a well executed project.

That is just plain awesome. I feel bad about his troubles finding software, hopefully being featured on HaD will help something surface.

Actually thats a good question. at least for my Xilinx Spartan-3E dev board (500K gates), you can add a different clock chip, up to and exceeding 100MHz, (stock is 50MHz) i think, but dont quote me. I haven’t had a need to yet. Might in the future though, who knows

This is Chris (the guy who made that).

@Jon: It only runs at 33 MHz because the multiplier implementation is slow. I was recently able to modify it to use the built-in multiplier blocks, and it now runs up to 50 MHz. Spartan3 chips are just slow, and the Virtex chips cost a small fortune.

@Biozz: It actually does support vector chaining, so it an peak at up to 3 FLOPS/cycle.

@Abbott – I’m not sure how much you know about circuit design, but the clock speed is determined by the maximum delay path. The critical path in my initial design was through the floating-point multiplier unit, as I was attempting to do 8 x 48-bit ADDs + a mux or two in the same cycle.

At 50 MHz, I think the critical path is the instruction-issue logic, which needs to perform quite a bit of conflict-detection.

For the entire design to work at a certain frequency, all signals must always set in time before the next clock cycle chimes in. The set times depend on the original design complexity, this particular Verilog/VHDL description, synthesis/optimization settings and on the hardware.

All modern FPGA’s have PLL or DLL modules that allow to get almost any arbitrary frequency from a limited selection of external fixed clock sources. So it does not really matter if the clock chip onboard is 100 or 50MHz, you can get up to 300MHz from either.

The real question is: Does the cooling system heat the seats surrounding the cray like it did in the original? ;-)

I’m 16 years post stroke. From the start I always consciously tried to use my affected hand to to tasks, but yet there’s plenty I can’t do yet, because the motor control is still lacking. This my get those who can’t even try to use their effected limb because of the injury, I just can’t see it restoring lost function.

Very cool!! Back in ’83 I worked at Digital Productions in LA and we used one of the Cray X-MP versions to make The Last Starfighter. I remember taking naps on the beast…. And the massive cooling tower & power converters it required.

Maybe some of the old DP folks might have code stashed away.

@D_ wrong article.

@cde: I’ve seen this a lot here lately. guessing database bug.

How much memory does it have?

Just wondering because I thought that it said in the article that it only had 4k words which is probably not enough for a real os.

Interesting.

After reading up on the Cray I got to wonder what would a CRAY one do if we ramped up the clock speed to to a modern 3.3 Ghz.

The sad thing is that it looks like per core an I7 will still beat it :(

Still way cool. I think you should make two more and give one to the folks working on GCC and on to the folks working on NetBSD.

You will get your OS and compiler then :)

I’d gathered that the wire lengths of the original Cray were set by the length of time it took for an operation to complete so that the previous operation would finish in the time it took the next one to travel down the wire. i don’t think only increasing the clock speed would work in that sort of tuned environment.

@David yes, that’s one of the amazing things about the Cray machines. Seymour Cray was one of those one in a million engineers who was just an order of magnitude better than anybody else, and his designs show it.

@J. Swift: Don’t forget, that this tiny Cray is 10 times smaller, so the wires are also 10x shorter, therefore this new design clock could be 10x faster before reaching the practical limits. :)

What is this? a Supercomputer for ants ?!