[John] has an interesting, if old piece of tech sitting on his workbench. It’s an Ohio Scientific C3-8P computer from the late 70s by way of a few garages, basements, and attics. As with most tech of this vintage, there are some problems, and [John] found debugging a little frustrating without the ability to trace and watch the programs. He needed a logic analyzer, and found one in an unlikely piece of hardware. [John] built one using a Teensy microcontroller, and further refinement of this project could turn it into a full in-system emulator.

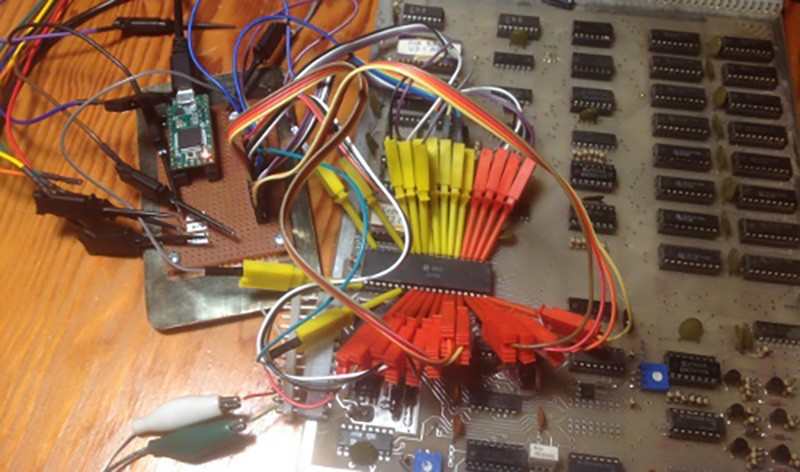

The old Ohio Scientific computer [John] is trying to bring back from the dead is based on the 6502 CPU. That’s sixteen address lines to monitor, eight data lines, and four control lines. These were wired directly to a Teensy 3.1.

Reading and controlling all the signals from a 6502 is a task that falls to Linux. A command line program controls the Teensy and is capable of reading memory, setting trigger addresses, dumping the entire address space to a file, or just recording the last 5,000 clock cycles. This kind of tech existed back in the late 70s and early 80s. It also cost a fortune. Now, with a $20 Teensy and probably another $30 in ribbon cables and test clips, anyone can build a logic analyser for a very old computer system.

Videos below.

Recognized that board the minute my browser opened :-) I recall the big analyzers from HP with disassembly and trace and so expensive they were rented! Nice job! I have one of the OSI with 18 or 20 full size expansion board slots that is having problems booting from floppies – 8 inch. And a Teensie around here somewhere……..

Check out osiweb.org if you haven’t already — there’s a forum too!

What I recognized was the configuration of those logic analyzer clips. Been there, done that! :-)

===Jac

This could also be very handy for repairing old arcade boards aswell.

I.E. Atari used the 6502 quite a bit, personally I have 3 6502 based atari machines.

Better than all those clips, might be a daughter board. Plug the daughterboard into the system’s motherboard, then the CPU into that. Same way the Commodore PET added a memory expansion, relevantly enough. Would require the 6502 to be in a socket, but that might well be handy for lots of reasons anyway. Would also mean he could add hardware in the middle, to emulate / arbitrate between the CPU and it’s bus.

That made me remember Glomper Clips all of the sudden: http://www.digikey.com/product-search/en/test-and-measurement/test-clips-ic/2294786

They were and still are quite expensive. $60 for a 40-DIP. I plan on putting a teensy daughter on my z80.

Yup, i was thinking about that to. Shouldn’t be too hard to wire up a .1″ ribbon cable to an intermediate socket.

I usually just grab a lump of FPGA for a logic analyser. If it needs to be five volt tolerant then I have a ‘Open Bench Logic Sniffer’ which is a lump of FPGA with level translators.

I don’t think I would want to go to the trouble of setting up Linux just for this.

Nice hack all the same.

Well? Did he fix it?

Yes…. The analyser showed me the software was stuck trying to move the floppy head to track zero.

That in turn lead me to a burned out 7417 buffer on the disk controller that drives the stepper motor.