[Clifford] presented a fully open-source toolchain for programming FPGAs. If you don’t think that this is an impressive piece of work, you don’t really understand FPGAs.

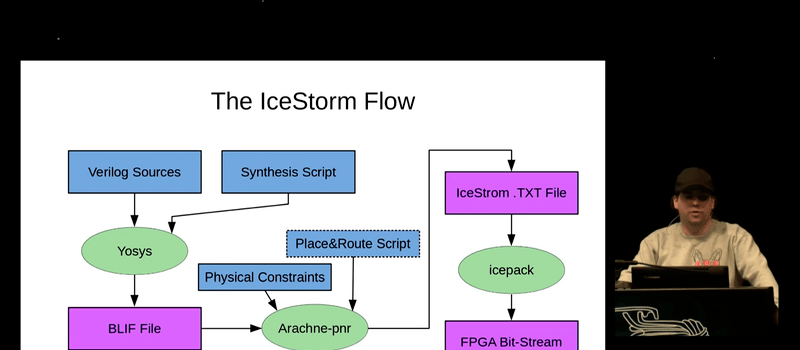

The toolchain, or “flow” as the FPGA kids like to call it, consists of three parts: Project IceStorm, a low-level tool that can build the bitstreams that flip individual bits inside the FPGA, Arachne-pnr, a place-and-route tool that turns a symbolic netlist into the physical stuff that IceStorm needs, and Yosys which synthesizes Verilog code into the netlists needed by Arachne. [Clifford] developed both IceStorm and Yosys, so he knows what he’s talking about.

What’s most impressive is that FPGAs aren’t the only target for this flow. Because it’s all open source and modifiable, it has also been used for designing custom ASICs, good to know when you’re in need of your own custom silicon. [Clifford]’s main focus in Yosys is on formal verification — making sure that the FPGA will behave as intended in the Verilog code. A fully open-source toolchain makes working on this task possible.

If you’ve been following along with [Al Williams]’s FPGA posts, either this introduction or his more recent intermediate series that are also based on the relatively cheap Lattice iCEStick development kit, this video is a must-watch. It’s a fantastic introduction to the cutting-edge in free FPGA tools.

Nice! A good open-source verilog synthesis program has been missing for years.

Now, can we do something about STA [Static Timing Analysis] and maybe some DRC/LVS, Optical Process Correction, and maybe some apps to view GDS/Milkyway DB’s?

Clifford is working on the iCE40 timing model and an STA pass in Yosys. I’m working on timing-driven routing and topological timing analysis in arachne-pnr. Please be patient, it’s on the way! (Or come help out…) Can’t help with the other stuff. :-)

keep on trucking man! The closed source nonsense (and buggy closed tools) that the major vendors do has turned me away from FPGAs. This is pretty exciting!

For those of us that don’t speak German: https://www.youtube.com/watch?v=SOn0g3k0FlE

Totally confused.

Those are just re-links to the CCC content, which is (at least here in Germany) entirely in the original English. :)

Interesting developments, but without support from the FPGA vendors, it still relies on reverse engineering of all the different FPGA variants, not only structurally, but also with respect to all the timing parameters.

I consider this very interesting project.

I think it does to FPGAs what Arduino did to Microcontrollers.

Cliffords work will get a lot of people started on the subject, and this is a GOOD thing.

In general clifford is a guy who really does things that make the world a more interesting and enjoyable pace.

He also started OpenSCAD a few years back (now maintained by marius kintel) and did a lot of other great projects in the past.

But THIS is really big and could be a total game changer in the FPGA industry.

Now that there are open toolchains the big players like altera will be forced to join the party.

In the end everybody, the vendors and their customers will benefit from it.

Thank you for spending your precious lifetime on projects like that!

You are one of my personal heroes.

overflo & clifford are one of my personal heroes!

Good work, Clifford & co.

I hope your Reverse engineering project is really based on clean room reverse engineering. Two or three years ago I visited Vienna and met this slender blonde young man in a hackerspace. He boasted to work with you on this project and showed some of his work. Back there he also showed the debug symbols and disassembly of the Lattice tools. I hope I misinterpreted this wrong and you really have a clean project.

i don’t think you need to worry here.

afaik mathias (the blonde guy you are reffering to) did a lot of basic research in that area and that information was the base to create documentation that was then used to implement the software tools clifford and others wrote.

so there is no direct link between what clifford built and what mathias was researching before that (as in: no lattice code went into this project in any way).

clifford started his work months before mathias did what he did, but it sure was a very useful inspiration and important for the project as whole.

so please dont get this wrong, i am not trying to suggest that mathias work was not important or something along that lines. it sure was. it is just not a part of the tools availalable right now.

the debug information in the lattice tools you mentioned to can enabled with a -debug parameter.