Spec sheets are an important tool in determining the performance of a given part or system, but they’re not the be all and end all when it comes to engineering. However, specs alone don’t prove whether a given system can complete a given task. Sometimes, you need to actually do the work to prove it instead – as [Sylvain] has done, running DOOM on the iCE40 FPGA.

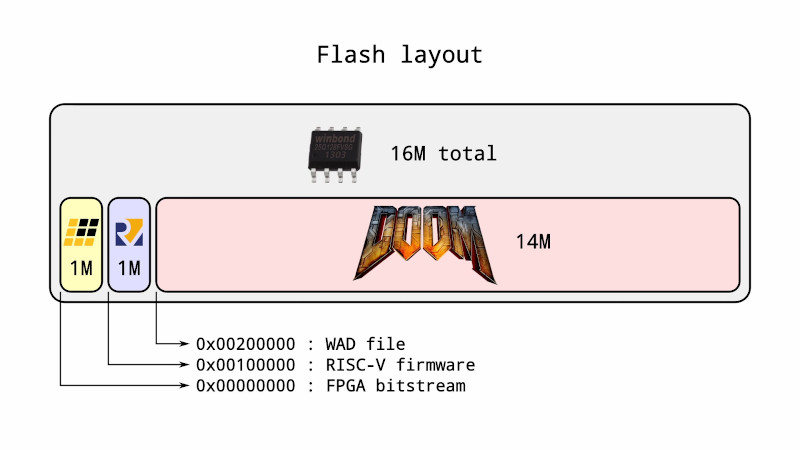

DOOM’s minimum specifications demand a 386 with 4MB RAM minimum, but it’s commonly agreed that a 486 DX2 running at 66MHz with 8MB of RAM is required to play the game smoothly. With an iCEBreaker v1.0b running a RISC V softcore at 25MHz, it may seem like a difficult task, but the RISC V core has the benefit that many instructions run in a single clock cycle that take many on the 486. While the iCEBreaker doesn’t have much RAM onboard, it’s a simple job to piggyback an 8MB SPI device on top of the existing flash storage. Control of the game is via keystrokes sent to the iCEBreaker over serial, while video is handled over a PMOD video interface with an HDMI connector.

[Sylvain] does a great job of explaining all the minute details of the work that was required to get things working, and has provided files on Github for those keen to replicate the feat or expand upon the code. Music is notably absent but MIDI output could likely be achieved without much hassle. “Does it run DOOM?” is still a question asked of many platforms, even the new Nintendo Game & Watch. Video after the break.

Dang that audio is hard to follow, sounds like he got a cheap 486 era multimedia kit microphone, and dipped it in coffee.

Ok, my pronunciation isn’t great (can’t completely blame the gear) and the mic is not a 1k$ setup but I didn’t think it was that bad. I have a new mic and audio interface on the way, hopefully that’ll help a bit.

Sounds fine to me?

Your pronunciation is absolutely fine.

Yah it’s not bad, I just assumed it would be easier on my ear if the higher frequencies weren’t clipped a bit, making the sibilants a little indistinct. It could be my hardware and the audio level on video combining to do that, on my laptop had to have all volume controls maxed to hear it.

There is a periodic high pitch chirp on the original recording, I have no idea where it came from and I only noticed after spending like 2h recording the voice track and didn’t want to re-do it. So I tried to notch it out but that definitely cut out part of the higher frequencies. (and didn’t even completely removed the chirp either …)

At least this actually runs doom unlike the game and watch, which is just some poorly written attempt at a raycaster and some ripped off graphics

Why so much negativity? It’s always cool to get it running in places that were never designed to have that sort of functionality. You have to do what you can within the restrictions you’re given.

They’re just telling the truth. The raytracing NES rom that’s purported to be “Doom” that’s shown running on the new Game & Watch is impressive. But it’s not Doom. It doesn’t have any of the same levels, graphics, enemies, weapons, music, or anything else that would qualify it as Doom. It’s a first person shooter NES demo. And that’s fine. But call it what it is. It’s not Doom not matter how much the creator wanted it to be in order to satisfy the “does it run doom” meme.

Next stop is XIP and lots of QSPI PSRAM?

Ok, MMU and a matching ISA will explode an UP5K.

A real *NIXish OS would be impossible!

Let’s ignore speed for a while.

Are FOSSy toolchains for bigger FPGAs stable enough to implement a CPU for a *NIX?

Or can it be done in multiple iCE40ers in one system?

When will we see a complete FOSSy *NIX on an FPGA system which is capable to rebuild itself without a PC as nanny?

Let it be slow and maybe need a weeks to completely rebuild itself.

For a while a PC as booster is ok.

Maybe the many FPGAs way would be even better for this, so the system only would have to build one flow at a time and if changes are incremental and compatible, it could evolve on its own.

I like that idea… but admittedly it still is far beyond my current capabilities…

…but that may change…

For a while I’l excercise a bit with smaller Ideas like TTA and such…

o;-) . o O ( ॐ!!! )

Been done:

https://hackaday.com/2019/04/19/pano-logic-fgpa-hacking-just-got-easier/

It’s definitely possible! Here is an example of someone doing it on an ECP5 board: https://twitter.com/fpga_dave/status/1053290842809683968

Linux can run on m68k (no MMU), so it’s entirely possible to run Linux on an iCE40. All it really needs is a few megabytes of RAM.

I’m gonna have to ask you to prove that, all m68k linux ports I know about require an MMU. When it’s said “It runs on an Amiga” it’s not meaning a bog stock A500 with a 68000.

The old μClinux port does support 68K with no MMU. Good luck building it though as you need to replicate the build environment of that time so kernel, libraries, compiler and all the tools need to be of similar vintage. No chance of getting a modern Linux version to run or even fit without lots of work.

An MMU is a tiny amount of logic, FPGA-wise – it’s just doing address translation. Getting access to a ton of memory and storage is pretty trivial for an FPGA if you have the I/O pins, and native block rams and DSP blocks even mean implementing things like caches and such is reasonable, the ‘hard’ part is just running with a high clock frequency. You can definitely implement a system that can reasonably run linux, it’s just going to run somewhere in the 50-200MHz range.

Well that’s the challenge here … the ice40 has none of that. Very limited IOs (like … 39 IOs _total_ and most of those are used for other things already). Very limited logic ( ~ 5000 LUT4s, that’s it, not a lot of BRAMs either ) and it’s slow fabric. 50 MHz, no way, 25 MHz is the best you can run a RISC-V core and I’m not even sure with the MMU if it’ll reach that.

How about something like the ECP5 PCI Express Development Kit?

It’s actually got quite a lot of IO pins brought out to what look like (but arn’t – mechanical compatibility only) two x16 pcie gold contact sets along the top – so you just make boards up with x16 connectors on them, and wire them how you want. There are two unpopulated 2×22 0.1″ headers also – could just use a wire-wrapping tool to make connections to the peripherals you want, without needing any PCBs.

And symbiflow has support for the 85k gate ECP5 on it, via project trellis.

They were rare in being a board with pcie support for <<$1k, (although the licensing had a 30 day evaluation time limit once activated – which sorta killed it for me at the time), but they become much more interesting now that project trellis exists… (project trellis is as icestorm, but for the ECP5 parts).

https://www.latticesemi.com/Products/DevelopmentBoardsAndKits/ECP5PCIExpressDevKit

Sure I got it running in a x68000 the real question is why did the non 030 not run it? I think it’s the global zone init.

> Ok, MMU and a matching ISA will explode an UP5K.

We’ll see about that …. :D

…having different CPU components (e.g. ALU, MMU, …) in different FPGAs wouldn’t make a big difference, just some more traces between the chips…

Pfff !

I will be impressed when somebody will actually run Doom on a vacuum valve computer with a CRT as display.

Or on a molecular Babbage analytical engine.