[Mark] starts a post from a bit ago with: “… maybe you have also heard that SystemVerilog is simply an extension of Verilog, focused on testing and verification.” This is both true and false, depending on how you look at it. [Mark] then explains what the differences are. It’s a good read if you are Verilog fluent, but just dip your toe into SystemVerilog.

Part of the confusion is that until 2009, there were two different things: Verilog and SystemVerilog. However, the SystemVerilog 2009 specification incorporates both languages, so modern Verilog is SystemVerilog and vice versa.

While many new features are aimed at verification, there is something for everyone. For example, [Mark] explains how you can replace instances of reg and wire with the logic data type. SystemVerilog will figure out if you need a reg or a wire on its own.

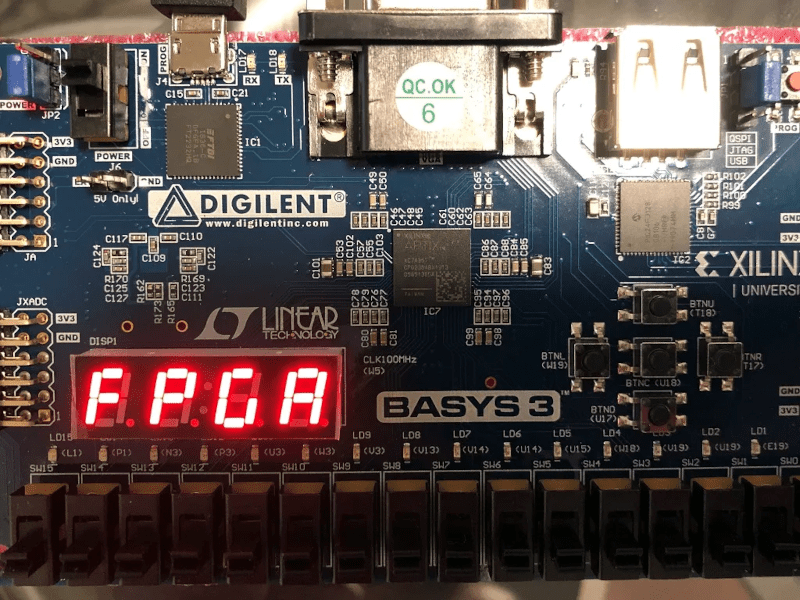

In addition, some common idioms are now part of the standard, which can make defining always blocks easier. So if you are using FPGAs and Verilog, are you using SystemVerilog? We don’t see much of it in incoming projects, but we do see it occasionally. Of course, pundits tell us that soon we won’t even have to write Verilog thanks to — what else? — AI. We remain skeptical.

As useful as SystemVerilog is, I find the features provided by the Emacs verilog-mode an almost complete substitution (and, in some regards, superior).

I encountered a strange case of plain Verilog not accepting a simple construction that looked perfectly legal to me, whereas when I switched to SV, there was no problem. So now, I always work in SV mode. (no, I don’t remember the code in question…)

I taught myself Verilog last year. I’m not sure the tools I was using supported SystemVerilog. I have one question, though. Verilog supports arrays like this:

wire [15:0]step[SIZE-1:0];

But you can’t pass an array to a module. It makes for a colossal amount of obfuscation by index arithmetic! So my question is, does SystemVerilog support passing arrays? If so, I would switch in a heartbeat if I could.

Yes, it does

Excellent!

@Al Williams asked: “What Is SystemVerilog, Really?”

Answering that question (IMHO) first begs an answer to a higher level question: What are the differences between the main modern Hardware Description Languages (HDLs)?

This seven year old article tries to answer that question. Yeah it’s a bit dated, but it gives you the view from 10,000 feet in a concise way:

What’s the Difference Between VHDL, Verilog, and SystemVerilog? Designing a complex SoC would be impossible without these three specialized hardware description languages. Rob Dekker, Sept. 17, 2014

https://www.electronicdesign.com/resources/whats-the-difference-between/article/21800239/whats-the-difference-between-vhdl-verilog-and-systemverilog

If you are a crusty old EE like me from the U.S., maybe you started with VHDL (in the beginning VHDL development was in-part funded by the U.S. Dept. of Defence [DoD]). But over the years I grew familiar working with other HDLs as well, not just VHDL. The opposite may be true for some people living outside the U.S. But VHDL still has a strong foothold in the EU. Today it seems lines between HDLs are rather blurred. Which is probably a good thing. I feel the HDLs are different enough to justify their separation.

Caveat: While I am trained in Combinational and Sequential Logic design and optimization, I use HDLs infrequently – so I’m no expert. Becoming an expert in HDL design really needs you to be doing it regularly (like every day). Every time I start a new CPLD/FPGA project, at first it feels like I’m starting over anew. It’s kind of like you thought you knew Regular Expressions in Perl-5, until you need to to jump back into it.

It might be useful to explain what SystemVerilog is: SystemVerliog is meant for describing what your design is supposed to do, instead of how to implement it, for use as a model. That’s why it’s so useful for testing: you run your test inputs through SystemVerilog or SystemC or whatever, verify there’s nothing really unexpected in the output of the model, then verify you get the same thing out of simulation from your synthesis.