From the Institute of Computing Technology division of the Chinese Academy of Sciences and Peng Cheng Laboratory comes a high-performance and well-documented RISC-V core called XiangShan.

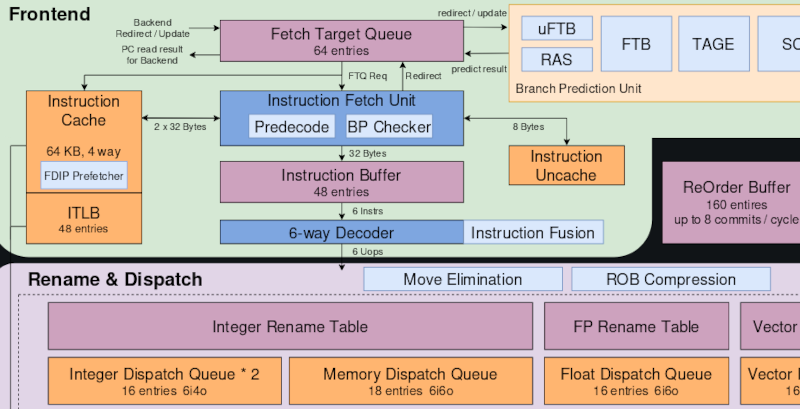

In the Git repository, you’ll find several branches including at least two stable branches: Yanqihu and Nanhu. The currently developed architecture, Kunminghu, is impressive, with a sophisticated instruction fetch unit, a reorder buffer, and a register renaming scheme.

The point of these types of circuits in a CPU is to allow multiple instructions to process at once. This also implies that instructions can be executed out of order. A cursory glance didn’t show any branch prediction logic, but that may be a limitation of the documentation. If there isn’t one, that would be an interesting thing to add in a fork if you are looking for a project.

On the computing side, the processor contains an integer block, a floating point unit, and a vector processor. Clearly, this isn’t a toy processor and has the capability to compete with serious modern CPUs.

There is a separate GitHub for documentation. It looks like they try to keep documentation in both Mandarin and English. You can also find some of the academic papers about the architecture there, too.

We love CPU design, and this is an interesting chance to contribute to an open CPU while there are still interesting things to do. If you need to start with something easier, plenty of small CPUs exist for educational purposes.

Looks like it has a branch prediction unit (top right yellow block in the diagram). I didn’t look at any code but it’s also on the README.md architecture diagram.

When I heard no prediction I did think they were going all in on a branchless coding paradigm but that’s be ludicrous I suppose.. eventually you have to loop. And probably very often in run of the mill parts of a system (strong processing etc).

Ah, you are right. Well, then I stand corrected. I was trying to think of something that might inspire someone to add to the project. On the other hand, you can always experiment with different branch prediction, different register “color” schemes, etc. So still plenty to do

They must have learnt that trick from Snowden’s wild false claims.

Interesting presentation at 36:00 https://youtu.be/4_R0S6piLA0

Direct link: https://youtu.be/4_R0S6piLA0?t=2160

While I doubt it can compete with modern CPUs it looks impressive.

Using TAGE branch predictors is IIRC pretty damn modern, though TAGE itself is very old now it’s just recently I’ve seen it actually used.

The integer throughput should be adequate however seriously limited by the dispatch queues.

Interesting and that’s coming from someone really disliking RISC V as an architecture (it’s just a rewarmed old RISC design IMO).

I always saw RISC-V as cherry picking the best of the best from all the expired patents that they could and mashing them together in a coherent fashion.

It is not even trying to compete with, say, current generation Intel or AMD. It is trying to get to where it can compete with ARM. Specifically the ARM Neoverse N2 with their faster design, and the A76 with the slower.

https://www.servethehome.com/xiangshan-high-performance-risc-v-processors-at-hot-chips-2024/o

So cellphone or Raspberry Pi equivalents rather than desktop or server. Except of course, that you can do light desktop computing with a Pi 5. Not high end gaming, CAD solvers, or other heavy number crunching unless you want to feel like you are stuck back in the last millennium.

But China is gravely concerned about being cut off from advanced microchips and is putting together multiple back up plans. It looks like this is the one to create a “good enough” application core that could be used in phones, manufacturing and military control and guidance systems, and even desktop computers if necessary.

They have other (mostly closed source) desktop and server chip designs. For example, they have built a multi core (dated) server (?) chip around IBM’s open sourced Power 64 cores derived from the A2 core. Basically 2010 era super computer / high speed data handling cores. But they hired enough IBM staff to recreate the entire 2010 era CPU.

Sorry, I posted the wrong link. It should be this:

https://www.servethehome.com/xiangshan-high-performance-risc-v-processors-at-hot-chips-2024/

“A cursory glance didn’t show any branch prediction logic, but that may be a limitation of the documentation.”

Branch prediction logic is clearly visible in the article’s “hero image”

High performance marks included in nios

They claim it is the “Highest performing open-source processor series by far” — what about OpenPower?

Hard to believe they have better performance than the 96 core, 4 GHZ Power9? (last fully Open chip)