For almost forty years, integrated circuits have become smaller and smaller. These chips started out with massive transistors in the early 1970s. They shrank to less than 1μm by 1990, and shrank yet again to less than 100nm by the turn of the last century. Now, Imec and Cadence are experimenting with 5nm technology – the smallest technology available for any mass-produced integrated circuit.

The history of microelectronic fabrication over the last decade is a story of failure. Something happened in 2005, and although chips could be designed at ever-smaller technologies, the transition to these smaller manufacturing processes didn’t go as smoothly as in the 70s, 80s, and 90s. Just a few years ago, Intel said 10nm chips would ship by 2015. These chips are nowhere to be found, and even 14nm technology is still catching up to the yields found in 22nm technology. In 2009, Nvidia said their flagship graphics card would be built with a 11nm process. The current Nvidia flagship desktop graphics card is built with 28nm technology. Moore’s law isn’t 18 months anymore.

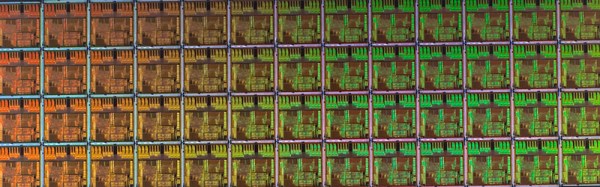

While Imec and Cadence have completed the tapeout on a 5nm device, it’s just a test chip. Before starting manufacturing on a single process node, Intel and others will tapeout a simple test chip to verify their latest process. This 5nm tapeout will not become a manufactured chip, but it does mean we’ll see more talk about the 5nm process in the future.