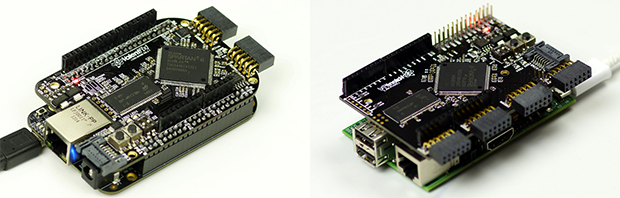

We’ve seen FPGA dev boards out the wazoo—even some following the current trend of putting an FPGA and an ARM processor on a single board. Take one good idea and mix it in with a few million Linux/ARM boards already piling up on workbenches the world over and you get LOGi: an FPGA designed to plug into the Raspberry Pi and BeagleBone.

Both the Raspberry Pi and BeagleBone versions of the LOGi feature a Spartan 6 FPGA with 9152 logic cells, 16 DSP Slices, 576KB of RAM, and 96 I/O Pins. There’s also 256 MB of SDRAM and a SATA connector. The Kickstarter has a few demos for this board, namely a machine vision, Bitcoin mining (though don’t expect this board to make return-on-investment with mining), and an autonomous vehicle control demo. The LOGi’s hardware is comparable to the Papilio Pro, so potential projects may include generating NTSC video, adding a VGA out, and a few retrocomputer emulations via OpenCores.

For what this Kickstarter asks for the Pi or ‘Bone version of the LOGi—$89 USD for either—you’ll get a surprisingly capable FPGA dev board that’s a bit cheaper than comparable offerings. Sure, you won’t save any money buying a Pi and a LOGi, but if you have a few Raspberries lying about, you could do much worse for a starter FPGA board.

Thanks [hamster] for sending this one in.

This is the same FPGA present in Bunnie’s NeTV hardware, where its used to decode (but not decrypt) the incoming HDMI signal, encrypt an overlay with the same HDCP key as the incoming video, mix the signals (color-keyed overlay), and re-encode the HDMI signal in realtime. Just to give you a few ideas about the things possible with this FPGA.

How can you decode a signal without decrypting it? If it’s a complicated answer I should go look it up, but I’m curious.

I’m hoping the NeTV can be modified to decrypt and strip the worthless HDCP completely and become a cheap version of an HD fury. HDCP has no use at all to users, and needs to be removed as soon as possible from your video sources.

I feel the same way… I’m a cord cutter and go out of my way to legally obtain the content that I watch. It’s offensive to me that I’m being penalized for this by limiting the devices I can use this content on. People who are pirating the content can do anything they want with it. Where is the logic in this situation?

I believe that the NeTV works by shadowing the key exchange between the two devices, so that it comes up with the same key as the sending device. At this point it *could* decrypt the input but doesn’t; it uses the stream cypher nature and the fact that the frame boundaries are outside the encryption to selectively replace bits which it has *encrypted* using the shadow key.

The LX9 has 576 Kb (bits) of block RAM, not KB (bytes) of block RAM. It also has 90 Kb of distributed RAM (which, of course, comes at the expense of usable logic blocks).

http://www.xilinx.com/support/documentation/data_sheets/ds160.pdf

Yep, a frequent error. Luckily the KS page is fine.

Maybe hardware emulation of old SGI workstations? How usable is the MIPS core? Would it be possible to do a full-speed emulation of an Onyx or maybe even an Indigo? Those were fun machines. The Onyx was really loud, I think it had over 30 fans. it needed 220V power and a room of its own. It would be quite a hack to have a full-speed emulation running on a cell phone battery.

Problem with the old SGI stuff is documentation… From the driver implementation in netbsd we might be able to implement an O2, and the Indys are unique in that they actually have public documentation. More or less everything else… you’re basically SOL, running an old unsupported OS on old undocumented hardware.

And there is nothing in the SGI OS that is worth while. you can do more on a old PC running linux today than you could on 50 Onyx machines. the OSS Blender is a better 3D software package than anything that SGI ever had.

That said, I’d love an old OnyX to strip it of it’s case. It would make a very cool filing cabinet.

Theres not enough resources in the LX9 to emulate the full chipset and cpu of something of that scale. Think more 6502 / Z80 retro computing. Usable SRAM is really 64KB because two of the 18 bits are for parity and thus don’t count.

They’re *intended* for parity, but you can use them for anything you want. If you’re implementing an 18-bit-word machine, for instance, you’re golden. :)

I like the look of this.

Anything that gets more people working with FPGAs is a good thing.

I’ve been wanting to do something with FPGA’s for a long time. I just need a problem that needs one as a part of the solution. Perhaps some audio DSP stuff.

Been thinking of getting into FPGAs so I can play with LVDS…

Busted monitors and laptops can be had for practically nothing, usually it’s everything BUT the LCD panel that is not working, trouble is that cheap micros have nowhere near the speed to communicate with them and the super cheap Chinese ASICs you can buy from ebay lack documentation and SW to program them…

This is also the same chip as the Mojo from Embedded Micro.

The picture freaked me out a bit, until I realised that it has been reversed. I’m ok, now…

Yeah, I thought the same. Though why does the one on the right looks like you can lay it on top the one on the left?

I have been using an Altera SocKit Cyclone 5 dev board recently: dual core ARM A9 supported by a Linux distro with 1G of DDR3 and a moderately large 110k element FPGA on the same die (though still somewhat independent – separate JTAG connections, etc.) also with it’s own 1G of DDR3. Not bad a bad deal for $300 I thought.

http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=816

FreeSoC Mini has uC, FPGA, AND reconfigurable analog circuits for $50 shipping now. Chip is $10 if you want to release something.

The real advantage to this device (at least on the bone version) is the fast coupling between the FPGA and the ARM chip. The bone exposes the external memory bus, giving 200MBytes/sec access (in theory) to the FPGA.

The only boards that give this level of I/o to my knowledge are the zynq (or cyclone soc) boards like the parallella or zed board, and they’re a lot more expensive than the combined cost of a logi board and a bone board.

Almost all the high-speed arm chips have pitifully slow gpio, and running Linux on them reduces their SPI interface down to a pathetic 12-15MHz. You’re still stuck with SPI if you’re using the raspberry PI, though :(

Hi,

unfortunately its not possible to reach the 200MB/s with the FPGA. We have connected the multiplexed bus and its safer to use a 50Mhz GPMC clock thus giving a max bandwidth (measured in user-space) of 70MB/s (max over multiple transaction) with our generic kernel driver (EDMA and burst access). Theoretical bandwidth with our settings is 76MB/s so you can get pretty close to this in kernel space and using interrupt to trigger transfer.

For the rapsberry-pi the max SPI clock is 32Mhz (higher give unstable transfer) and we get up to 3.9MB/s. Its enough for control application and low freq signal processing.

Thanks Jpiat – You have just given me a reason to get a Bone. 70MB/s is going to be great for a few projects I have lots of ideas for, but not enough host/FPGA bandwdith.

If Zedboard is too expensive, check out Zybo — it’s the smaller brother of Zed.

@Simon

“The only boards that give this level of I/o to my knowledge are the zynq (or cyclone soc) boards like the parallella or zed board, and they’re a lot more expensive than the combined cost of a logi board and a bone board.”

Not sure where you got that idea from. From what I can see, the Parallella would still be cheaper. Price for the Beaglebone is $89, price for the LOGi that works with it is also $89, making a total cost of $178. In comparison, the Parallella pre-orders (when they were running) were $99.