There are very few ‘recent’ FPGAs out there that can be easily soldered. Due to their important number of IOs, they usually come in Ball Grid Array (BGA) packages. The Xilinx Spartan 6 LX9, a TQFP144 FPGA (having pins with a 0.5mm pitch) is one of the few exceptions that can be used to make low end development boards. However, it doesn’t have a lot of logic and memory resources or an on-chip Memory Control Block implemented in the silicon. Therefore, [Michael] designed an SDRAM controller with a small footprint for it.

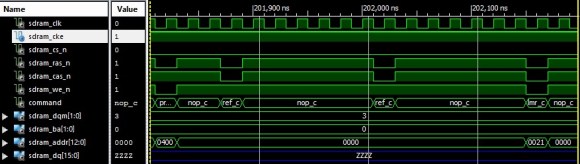

Writing an SDRAM controller from scratch isn’t for the fainthearted – first of all you really have to know how SDRAM works (RAS, CAS, precharges, refresh cycles), and because of the high speed and accurate timing required you also have to learn some of the finer points of FPGA off-chip interfacing. In addition, most publicly available open cores are very complex – for example just the RTL core of the sdr_ctrl controller on opencores.org adds up to over 2,700 lines of Verilog. Even if it is not an accurate comparison metric, [Michael]’s controller is only 500 lines long.