Designing a computer from scratch is one of the holy grails of hardware design. For programmable logic, designing your own processor is a huge accomplishment. That’s exactly what [zhemao] has done. He created EZ8, an 8 bit processor is written in Verilog. EZ8 has a 3 stage pipeline, which makes design very interesting. Instruction set pipelines have been used in processors for many years. They speed up operation by allowing the processor to execute more than one instruction in parallel. The idea is similar to washing, drying and folding laundry. Most people pipeline their laundry. One load is in the washer, another in the dryer, and a third is being folded. Pipelines aren’t a free lunch though – there are hazards. If one instruction requires the result of an instruction which is still being executed in parallel, there’s a problem. In our laundry analogy this would be like having one sock on the folding table while its mate is still in the dryer. The folding operation must wait for the drying operation to complete before the socks can be paired. This is exactly how assemblers handle the situation – they insert NOPs between known hazard instructions.

[zhemao] didn’t just give us a processor and no support though. He also included an assembler written in OCaml, and an emulator written in C. Several test assembly programs are also up on [zhemao’s] github repo to verify operation. [zhemao] has tested his processor with Altera Cyclone 5 series FPGAs, but it should be possible to port it to other FPGA manufacturers. If you want more information, [zhemao] also has a discussion going on in the ECE subreddit.

[Thanks for the tip LongHornEngineer!]

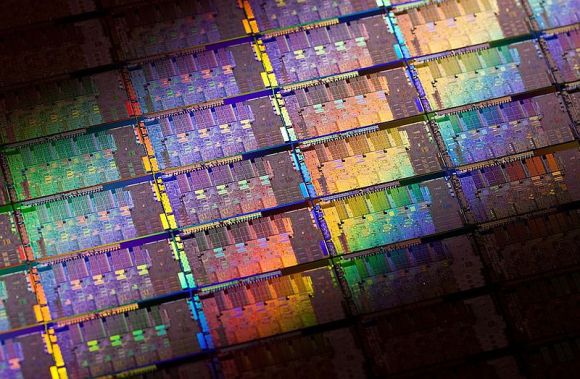

[Image courtesy of intel]