[Robert Baruch] wanted to tackle a CPU project using an FPGA. One problem you always have is you can either mimic something that has tools and applications or you can go your own way and just build everything from scratch (which is much harder).

[Robert] took the mimic approach–sort of. He built a CPU with the express idea of running Infocom’s Z-machine virtual machine, which allows it to play Zork. So at least when you are done, you don’t have to explain to your non-tech friends that it only blinks an LED. Check out the video, below, for more details.

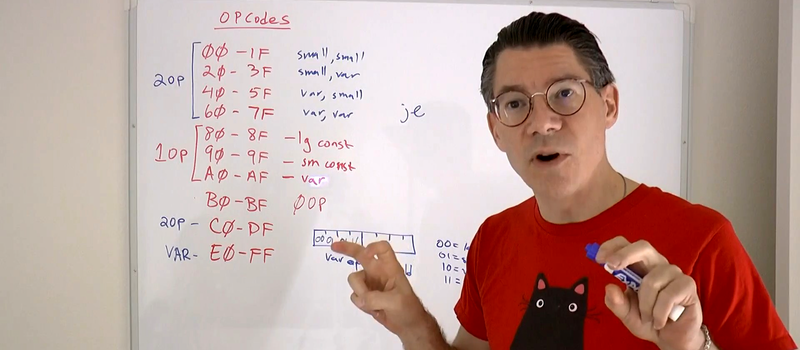

If it were just the Z-machine on an FPGA, we’ve seen that before. We’ve also seen people take the long road and build up everything around their custom CPUs. What makes this interesting is a very detailed set of videos describing the CPU and how it came to life.

We don’t mean there’s a five-minute video describing the CPU. Each of the six videos are substantial (most are longer than 40 minutes) and [Robert] walks through the Verilog code, using the Xilinx tools, and simulation. There are more videos to go, but with about four hours of video in the can, you might want to get a head start and watch them now.

If you’ve ever wanted to watch over someone’s shoulder while they are doing a significant Verilog FPGA design, this is your chance. We’ve seen the end result done before. If you want a peek at how it is to build the CPU and all new tools, A2Z is a good example of that. Maybe someone will port Zork to it soon.

This reminds me a little of something Western Digital did in the early 80s: they made a CPU that directly ran P-code, which was the intermediate language generated by Pascal compilers.

Just one thing, though: if the PDP-10 was a “minicomputer”, I wonder what [Robert Baruch] thinks constitutes a mainframe.

–> Pascal MicroEngine

“Just one thing, though: if the PDP-10 was a “minicomputer”, I wonder what [Robert Baruch] thinks constitutes a mainframe.”

That’s what everyone called them at the time. Mainframes were the room-sized IBMs.

Our PDP-10 at UC Irvine WAS room-sized. Every bit as big as a mid-sized System360.

I would assume because a crap load of expansions and peripherals.

Well, sure, it’s all relative. Our DECsystem 20 (which will always be a “PDP-10” to me) had two KA10 CPUs, which were three cabinets each, but by the time you added memory and I/O controllers it was twelve cabinets. Then add three 9-track tape drives, card punch, card reader, two POS Mohawk line printers, and about eight disk drives, and it’s a definite roomful. Add to that a few dozen terminals (TOPS-20 ran time sharing and batch concurrently), and it’s a BIG roomful. But I’ve seen PDP-11s that were decked out almost as big; what really made the PDP-10 a mainframe computer was 36-bit word, 256 Kword address space, floating point hardware, and s-tons of I/O bandwidth. Only next to a CDC Cyber series is it even remotely “mini”.

All of which has nothing to do with building CPUs in FPGAs to emulate virtual machines in hardware. But as a semi-relevant side-note, DEC’s final KS-10 CPU was implemented using AMD bit-slice ALUs, but this was a downgrade from the ECL-based KL10.

Ditto, though at the time they were branded as DECSYSTEM 10, https://en.wikipedia.org/wiki/PDP-10

Wikipedia describes the PDP-10 as a mainframe. I suppose it’s all relative.

The ones I recall from the time were small, three or four cabinet machines that were owned by engineering departments, and were referred to as minicomputers, while the corporate big iron (on which a few legacy batch jobs for engineering were still done) was called the mainframe. The former was used with terminals while the latter still had to be dealt with via punch cards.